### ISL98607

High Efficiency Power Supply for Small Size Displays

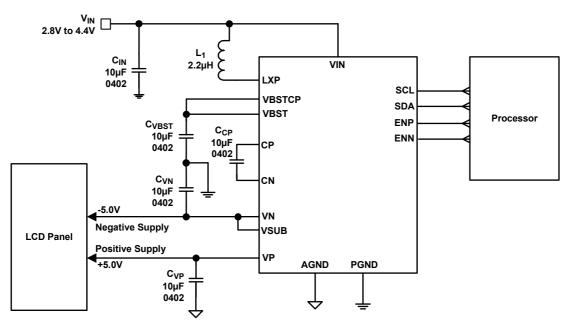

The <u>ISL98607</u> is a high efficiency power supply for small size displays, like smart phones, requiring ±supply rails. It integrates boost regulator, LDO, and inverting charge pump that are used to generate two output rails: +5V (default) and -5V (default). The ±5V output voltages can be adjusted up to ±5.7V with 50mV steps using the I<sup>2</sup>C interface.

The ISL98607 integrates synchronous rectification MOSFETs for the boost regulator and inverting charge pump, which maximizes conversion efficiency.

The ISL98607 integrates all compensation and feedback components, which minimizes BOM count and reduces the solution PCB size to 21mm<sup>2</sup>.

The input voltage range, high efficiency operation, and also very low shutdown current make the device ideal for use in single cell Li-ion battery operated applications.

The ISL98607 is offered in the 1.82x2.15mm WLCSP and 20 Ld 3x4mm TQFN packages, and the device is specified for operation across the -40°C to +85°C ambient temperature range.

### **Related Literature**

For a full list of related documents, visit our website:

• ISL98607 device page

#### **Features**

- · Two outputs:

- VP = +5.0V (default)

- VN = -5.0V (default)

- 2.8V to 4.4V Input voltage range

- >85.5% Efficiency with 12mA load between VP and VN

- 21mm<sup>2</sup> Solution PCB area

- Fully integrated FETs for synchronous rectification

- · Integrated compensation and feedback circuits

- I<sup>2</sup>C adjustable output voltages and settings

- Integrated VP/VN discharge resistors

- 1µA shutdown supply current

- · Multiple package options:

- 1.82x2.15mm, 4x5 array WLCSP with 0.4mm pitch

- o 20 Ld 3x4mm TQFN

- Pb-Free (RoHS compliant)

### **Applications**

- TFT-LCD Smart phone displays

- · Small size/handheld displays

Figure 1. Typical Application Circuit: TFT-LCD Smart Phone Display

## **Contents**

| 1.   | Overview                                      |

|------|-----------------------------------------------|

| 1.1  | Block Diagram                                 |

| 1.2  | Ordering Information                          |

| 1.3  | Pin Configurations                            |

| 1.4  | Pin Descriptions                              |

| 2.   | Specifications                                |

| 2.1  | Absolute Maximum Ratings                      |

| 2.2  | Thermal Information 5                         |

| 2.3  | Recommended Operation Conditions              |

| 2.4  | Electrical Specifications6                    |

| 3.   | Typical Performance Curves                    |

| 4.   | Application Information                       |

| 4.1  | I <sup>2</sup> C Digital Interface            |

| 4.2  | Write Operation                               |

| 4.3  | Read Operation                                |

| 4.4  | Register Descriptions and Addresses           |

| 4.5  | Register Functions                            |

| 4.6  | Register Map                                  |

| 4.7  | Output Voltage Setting                        |

| 4.8  | VP and VN Headroom Voltage and Output Current |

| 4.9  | Regulator Output Enable/Disable               |

| 4.10 | Negative Charge Pump Operation (VN)           |

| 4.11 | l PFM                                         |

| 4.12 | Pault Protection and Monitoring               |

| 4.13 | · ·                                           |

| 4.14 | Enable Timing Control Options                 |

| 4.15 | 5 VP Output Hi-Z Mode                         |

| 4.16 | 6 Component Selection                         |

| 5.   | General Layout Guidelines                     |

| 5.1  | ISL98607 Specific Layout Guidelines           |

| 6.   | Revision History                              |

| 7.   | Package Outline Drawings                      |

ISL98607 1. Overview

### 1. Overview

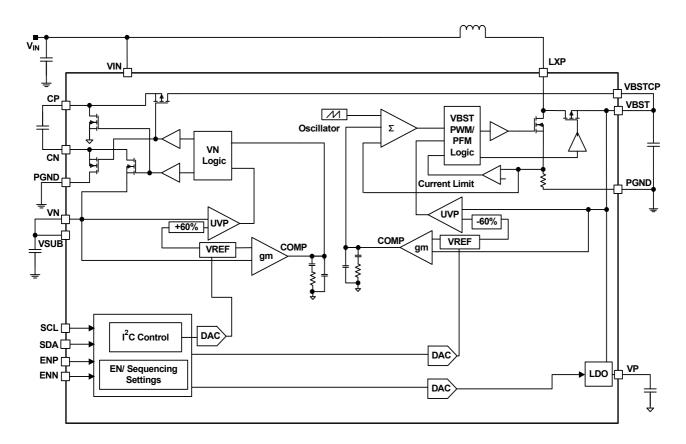

### 1.1 Block Diagram

### 1.2 Ordering Information

| Part Number<br>( <u>Note 4</u> ) | Part<br>Marking               | Temp Range (°C)              | Tape and Reel<br>(Units) ( <u>Note 1</u> ) | Package<br>(RoHS Compliant            | Pkg. Dwg. # |  |  |  |

|----------------------------------|-------------------------------|------------------------------|--------------------------------------------|---------------------------------------|-------------|--|--|--|

| ISL98607EIAZ-T (Note 2)          | 607A                          | -40 to +85                   | 3k                                         | 20 Ball (4x5 bump, 0.4mm pitch) WLCSP | W4x5.20E    |  |  |  |

| ISL98607IRTZ-T(Note 3)           | 8607                          | -40 to +85                   | 6k                                         | 20 LD 3x4 TQFN                        | L20.3x4A    |  |  |  |

| ISL98607-EVZ                     | ISL98607EIA                   | SL98607EIAZ Evaluation Board |                                            |                                       |             |  |  |  |

| ISL98607IRTZ-EVZ                 | ISL98607IRTZ Evaluation Board |                              |                                            |                                       |             |  |  |  |

#### Notes:

- 1. See TB347 for details about reel specifications.

- These Pb-free WLCSP packaged products employ special Pb-free material sets; molding compounds/die attach materials and SnAgCue1 solder ball terminals, which are RoHS compliant and compatible with both SnPb and Pb-free soldering operations. Pb-free WLCSP packaged products are MSL classified at Pb-free peak reflow temperatures that meet or exceed the Pb-free requirements of IPC/JEDEC J-STD-020.

- 3. These Pb-free plastic packaged products employ special Pb-free material sets, molding compounds/die attach materials, and 100% matte tin plate plus anneal (e3 termination finish, which is RoHS compliant and compatible with both SnPb and Pb-free soldering operations). Pb-free products are MSL classified at Pb-free peak reflow temperatures that meet or exceed the Pb-free requirements of IPC/JEDEC J-STD-020.

- 4. For Moisture Sensitivity Level (MSL), see the ISL98607 device page. For more information about MSL, see TB363.

ISL98607 1. Overview

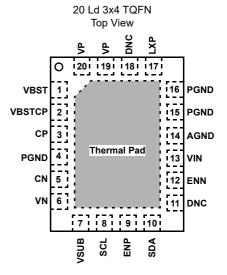

### 1.3 Pin Configurations

20 Bump, 4x5 ARRAY, 0.4mm Pitch WLCSP Top View

### 1.4 Pin Descriptions

| Pin Number<br>(WLCSP) | Pin Number (TQFN) | Pin Name       | Description                                                                                                                                                      |

|-----------------------|-------------------|----------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| A1, B1                | 15, 16            | PGND           | Power ground for the boost converter.                                                                                                                            |

| A2, E1                | 11, 18            | DNC            | Do not connect to external circuitry. This pin should be left floating.                                                                                          |

| A3, A4                | 19, 20            | VP             | VP Output. Connect a 10μF capacitor to ground. The VP pins must always be shorted together on the PCB.                                                           |

| B2                    | 17                | LXP            | Switch node for boost converter. Connect an inductor between the VIN and LXP pins for boost converter operation.                                                 |

| В3                    | 1                 | VBST           | Boost Converter Output. The boost converter output supplies the power to the negative charge pump and LDO. Connect a 10µF capacitor to ground.                   |

| B4                    | 2                 | VBSTCP         | Charge pump input. This pin must be connected to VBST on the PCB, so that the boost regulator provides the input voltage supply for the charge pump.             |

| C1                    | 14                | AGND           | Analog ground.                                                                                                                                                   |

| C2                    | 12                | ENN            | VBST and VN enable input. Note, this pin has 200kΩ (typical) pull-down to AGND.                                                                                  |

| C3                    | 9                 | ENP            | VBST and VP enable input. Note, this pin has $200k\Omega$ (typical) pull-down to AGND.                                                                           |

| C4                    | 3                 | CP             | Charge pump positive connection. Place a capacitor between CP and CN to create the VN voltage.                                                                   |

| D1                    | 13                | VIN            | Input Supply. Connect a 10µF capacitor to ground.                                                                                                                |

| D2                    | 10                | SDA            | Serial Data Connection for the I <sup>2</sup> C Interface.                                                                                                       |

| D3                    | 8                 | SCL            | Serial Clock Connection for the I <sup>2</sup> C Interface.                                                                                                      |

| D4                    | 4                 | PGND           | Power ground for the negative charge pump.                                                                                                                       |

| E2                    | 7                 | VSUB           | Substrate connection. VSUB must be the most negative potential on the IC, connect VSUB to VN.                                                                    |

| E3                    | 6                 | VN             | Negative charge pump output. Connect a 10μF capacitor to ground. Connecting two 10μF capacitors to ground lowers the negative charge pump output voltage ripple. |

| E4                    | 5                 | CN             | Charge pump negative connection. Place a capacitor between CP and CN to generate the VN voltage.                                                                 |

| N/A                   | -                 | Thermal<br>Pad | Connect to ground plane on PCB to maximize the thermal performance.                                                                                              |

ISL98607 2. Specifications

## 2. Specifications

### 2.1 Absolute Maximum Ratings

| Parameter                                      | Minimum  | Maximum    | Unit |

|------------------------------------------------|----------|------------|------|

| VBST, VBSTCP, CP, VP to AGND                   | -0.3     | 7          | V    |

| VN, VSUB to AGND                               | +0.3     | -7         | V    |

| VIN, SCL, SDA, ENN, ENP to AGND                | -0.3     | 6          | V    |

| LXP to AGND                                    | -0.3     | VBST + 0.3 | V    |

| CN to AGND                                     | VN - 0.3 | PGND + 0.3 | V    |

| Maximum Average Current Out of VBST Pin        |          | 1          | А    |

| Maximum Average Current Into LXP Pin           |          | 1          | А    |

| Maximum Average Current Into CN, CP Pin        |          | -1         | А    |

| ESD Rating                                     | Va       | Unit       |      |

| Human Body Model (Tested per JESD22-A114)      |          | 2          | kV   |

| Machine Model (Tested per JESD22-A115)         | 2        | V          |      |

| Charged Device Model (Tested per JESD22-C101)  | 7        | V          |      |

| Latch-Up (Tested perJESD78; Class II, Level A) | 1        | mA         |      |

### 2.2 Thermal Information

| Thermal Resistance (Typical)            | θ <sub>JA</sub> (°C/W) | θ <sub>JC</sub> (°C/W) |

|-----------------------------------------|------------------------|------------------------|

| 4x5 Bump 0.4mm pitch WLCSP (Notes 5, 6) | 66                     | 0.95                   |

| 20 Ld 3x4 TQFN (Notes 5, 7)             | 48                     | 16                     |

#### Notes:

<sup>7.</sup> For  $\theta_{\text{JC}}$ , the "case temp" location is the center of the exposed metal pad on the package underside.

| Parameter                    | Minimum          | Maximum | Unit |  |  |  |

|------------------------------|------------------|---------|------|--|--|--|

| Maximum Junction Temperature |                  | +125    | °C   |  |  |  |

| Storage Temperature Range    | -65              | +150    | °C   |  |  |  |

| Pb-Free Reflow Profile       | see <u>TB493</u> |         |      |  |  |  |

### 2.3 Recommended Operation Conditions

| Parameter                                  | Minimum | Maximum | Unit |

|--------------------------------------------|---------|---------|------|

| Ambient Temperature Range                  | -40     | +85     | °C   |

| VIN                                        | 2.8     | 4.4     | V    |

| VP                                         | +5      | +5.7    | V    |

| VN                                         | -5      | -5.7    | V    |

| VBST                                       | +5.15   | +6.0    | V    |

| Output Current Maximum (between VP and VN) |         | 100     | mA   |

θ<sub>JA</sub> is measured in free air with the component mounted on a high-effective thermal conductivity test board with "direct attach" features.

See <u>TB379</u>.

<sup>6.</sup> For  $\theta_{\text{JC}},$  the "case temp" location is taken at the package top center.

ISL98607 2. Specifications

### 2.4 Electrical Specifications

$V_{IN}$  = 3.7V, unless otherwise noted. Typical specifications are characterized at  $T_A$  = +25°C unless otherwise noted. **Boldface limits apply across the operating temperature range, -40°C to +85°C.**

| Parameter                                    | Symbol Test Conditions |                                                                                                                  | Min<br>( <u>Note 8</u> ) | Тур      | Max<br>( <u>Note 8</u> ) | Unit |

|----------------------------------------------|------------------------|------------------------------------------------------------------------------------------------------------------|--------------------------|----------|--------------------------|------|

| General                                      |                        |                                                                                                                  | I                        | l        |                          |      |

| V <sub>IN</sub> Supply Voltage Range         | $V_{IN}$               |                                                                                                                  | 2.8                      |          | 4.4                      | V    |

| V <sub>IN</sub> Supply Current               | I <sub>IN</sub>        | ENP = ENN = 3.7V<br>Enabled, LXP not switching                                                                   |                          | 620      | 900                      | μA   |

| V <sub>IN</sub> Supply Current When Shutdown | I <sub>SHUTDN</sub>    | ENP = ENN = 0V                                                                                                   |                          | 1        | 3                        | μA   |

| Undervoltage Lockout Threshold               | V <sub>UVLO</sub>      | V <sub>IN</sub> rising                                                                                           | 2.40                     | 2.52     | 2.65                     | V    |

| Undervoltage Lockout Hysteresis              | V <sub>UVLO HYS</sub>  | 5ms falling                                                                                                      |                          | 216      |                          | mV   |

| Boost Regulator (VBST)                       | · · · · ·              |                                                                                                                  | 1                        |          |                          |      |

| VBST Output Voltage                          | V <sub>VBST</sub>      | Register VBST_OUT = 0x00, no load                                                                                |                          | 5.15     |                          | V    |

| Boost nFET Current Limit                     | I <sub>LIM_VBST</sub>  |                                                                                                                  | 1.2                      | 1.4      | 1.8                      | Α    |

| Low-Side Switch ON-Resistance                | r <sub>ON_VBSTH</sub>  | T <sub>A</sub> = +25°C, I <sub>LOAD_VBST</sub> = 100mA,<br>LXP to PGND                                           |                          | 137      |                          | mΩ   |

| High-Side Switch ON-Resistance               | r <sub>ON_VBSTL</sub>  | T <sub>A</sub> = +25°C, I <sub>LOAD_VBST</sub> = 100mA,<br>LXP to VBST                                           |                          | 220      |                          | mΩ   |

| LXP Leakage Current                          | I <sub>L_LXP</sub>     | VLXP = 6V, ENP = ENN = 0V                                                                                        |                          |          | 10                       | μΑ   |

| Boost Minimum Duty Cycle                     | D <sub>MIN</sub>       | Boost frequency = 1.45MHz                                                                                        |                          | 12.5     |                          | %    |

| Boost Maximum Duty Cycle                     | D <sub>MAX</sub>       | Boost frequency = 1.45MHz                                                                                        |                          | 91       |                          | %    |

| Boost Switching Frequency                    | f <sub>SWV_VBST</sub>  | Boost frequency = default                                                                                        | 1.3                      | 1.45     | 1.6                      | MHz  |

| Boost Soft-Start Time                        | t <sub>SS_VBST</sub>   | C <sub>VBST</sub> = 10μF (not derated), V <sub>IN</sub> > V <sub>UVLO</sub>                                      |                          | 0.7      | 2                        | ms   |

| Negative Regulator (VN)                      |                        |                                                                                                                  |                          | I.       | <u> </u>                 |      |

| VN Output Voltage                            | $V_{VN}$               | VN_OUT = 0x00, no load                                                                                           |                          | -5       |                          | V    |

| VN Output Voltage Accuracy                   | V <sub>ACC_VN</sub>    | VN_OUT = 0x00, VBST_OUT = 0x00,<br>-30mA < I <sub>LOAD_VN</sub> < 0mA                                            | -2                       |          | 2                        | %    |

| Charge Pump Switching Frequency              | f <sub>SW_VN</sub>     | CP Frequency = default, 50% duty cycle                                                                           | 1.3                      | 1.45     | 1.6                      | MHz  |

| Charge Pump Leakage Current                  | I <sub>L_CP</sub>      | CP pin, CP = 6V, ENN = 0V                                                                                        |                          |          | 10                       | μΑ   |

| VN Discharge Resistance                      | R <sub>DCH_VN</sub>    | VN = -1V                                                                                                         |                          | 35       |                          | Ω    |

| VN Soft-Start Time                           | t <sub>SS_VN</sub>     |                                                                                                                  |                          | 0.7      | 2                        | ms   |

| Positive Regulator (VP)                      |                        |                                                                                                                  | I.                       | <u>I</u> |                          |      |

| VP Output Voltage                            | V <sub>VP</sub>        | VBST_OUT = 0x00, No Load                                                                                         |                          | 5        |                          | V    |

| VP Output Voltage Accuracy                   | V <sub>ACC_VP</sub>    | VP_OUT = 0x00, VBST_OUT = 0x00,<br>0mA < I <sub>LOAD_VP</sub> < 30mA                                             | -2                       |          | 2                        | %    |

| VP Dropout Voltage                           | V <sub>DRP_VP</sub>    | I <sub>LOAD_VP</sub> = 100mA                                                                                     |                          |          | 100                      | mV   |

| VP Leakage Current                           | I <sub>L_VP</sub>      | VP pin, VP = 0V, ENP = 0V                                                                                        |                          |          | 2                        | μA   |

| VP Discharge Resistance                      | R <sub>DCH_VP</sub>    | VP = 1V                                                                                                          |                          | 80       |                          | Ω    |

| VP Soft-Start                                | t <sub>SS_VP</sub>     |                                                                                                                  |                          | 0.7      | 2                        | ms   |

| Protection                                   |                        | 1                                                                                                                | 1                        | 1        |                          |      |

| Thermal Shutdown Temperature                 | T <sub>OFF</sub>       | Die temperature (rising) when the device will disable/shutdown all outputs until it cools by T <sub>HYS</sub> °C |                          | 130      |                          | °C   |

| Thermal Shutdown Hysteresis                  | T <sub>HYS</sub>       | Die temperature below T <sub>OFF</sub> °C when the device will re-enable the outputs after shutdown              |                          | 10       |                          | °C   |

| VP Undervoltage Protection Threshold         | V <sub>UVP_VP</sub>    |                                                                                                                  |                          | 0.6 x VP |                          | V    |

| VN Undervoltage Protection Threshold         | V <sub>UVP_VN</sub>    |                                                                                                                  |                          | 0.6 x VN |                          | V    |

ISL98607 2. Specifications

$V_{IN}$  = 3.7V, unless otherwise noted. Typical specifications are characterized at  $T_A$  = +25°C unless otherwise noted. **Boldface limits apply across the operating temperature range, -40°C to +85°C. (Continued)**

| Parameter                            | Symbol           | Test Conditions    | Min<br>(Note 8) | Тур | Max<br>(Note 8) | Unit |

|--------------------------------------|------------------|--------------------|-----------------|-----|-----------------|------|

| Logic/Digital                        |                  |                    |                 |     |                 |      |

| Logic Input Low Voltage              | $V_{IL}$         | ENN, ENP, SCL, SDA |                 |     | 0.4             | V    |

| Logic Input High Voltage             | V <sub>IH</sub>  | ENN, ENP, SCL, SDA | 1.1             |     |                 | V    |

| I <sup>2</sup> C SCL Clock Frequency | f <sub>CLK</sub> | ( <u>Note 9</u> )  |                 |     | 400             | kHz  |

| Debounce Time                        | t <sub>d</sub>   | ENN, ENP           |                 | 10  |                 | μs   |

| Internal Pull-Down Resistance        | R <sub>EN</sub>  | ENN, ENP           |                 | 200 |                 | kΩ   |

#### Notes:

<sup>8.</sup> Parameters with MIN and/or MAX limits are 100% tested at +25°C, unless otherwise specified. Temperature limits established by characterization and are not production tested.

<sup>9.</sup> For more detailed information regarding I<sup>2</sup>C timing characteristics see <u>Table 1 on page 10</u>.

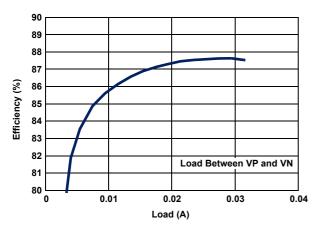

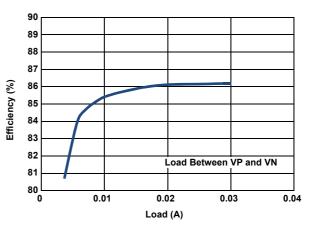

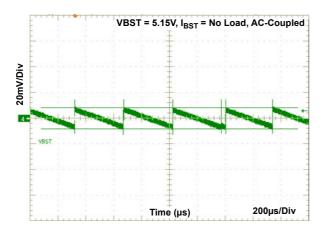

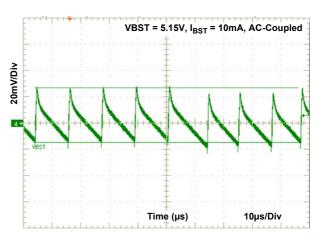

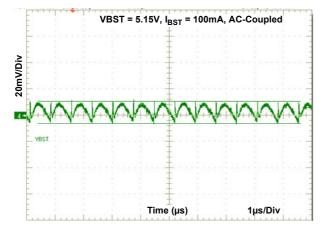

### 3. Typical Performance Curves

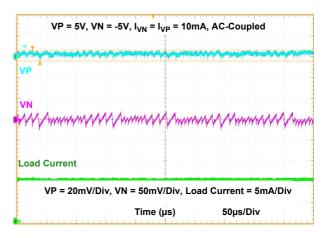

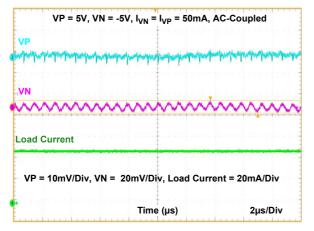

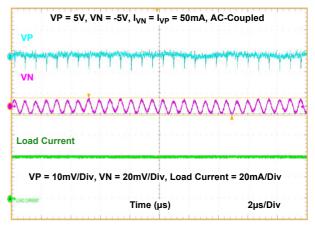

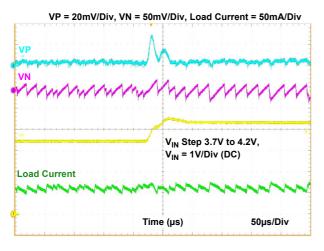

$T_{A} = +25 ^{\circ}\text{C}, \ V_{IN} = 3.7 \text{V}, \ \text{Registers VP\_OUT}, \ \text{VN\_OUT and VBST\_OUT} = 0 \text{x} 00, \ \text{DFE252012C} \ (2.5 \text{mmx2mm}) \ \text{Toko Inductor}, \ C_{VBST} = 10 \mu \text{F}/0402, \ C_{VP} = 10 \mu \text{F}/0402 \ \text{and} \ C_{VN} = 2 \ \text{x} \ 10 \mu \text{F}/0402 \ \text{unless otherwise noted}.$

Figure 2. Efficiency vs Load - Register 0x0D = 0x04, Register 0x0F = 0xDF

Figure 3. Efficiency vs Load - Register 0x0D = 0x34, Register 0x0F = 0xDA

Figure 4. VBST Output Voltage Ripple with No Load

Figure 5. VBST Output Voltage Ripple with 10mA Load

Figure 6. VBST Output Voltage Ripple with 100mA Load

Figure 7. VP and VN Output Voltage Ripple - 10mA Load

$T_{A}=+25^{\circ}\text{C},\ V_{IN}=3.7\text{V},\ \text{Registers VP\_OUT},\ \text{VN\_OUT and VBST\_OUT}=0\text{x}00,\ \text{DFE}252012\text{C}\ (2.5\text{mmx}2\text{mm})\ \text{Toko Inductor},\ C_{VBST}=10\mu\text{F}/0402,\ C_{VP}=10\mu\text{F}/0402\ \text{and}\ C_{VN}=2\ \text{x}\ 10\mu\text{F}/0402\ \text{unless otherwise noted}.\ \textbf{(Continued)}$

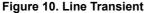

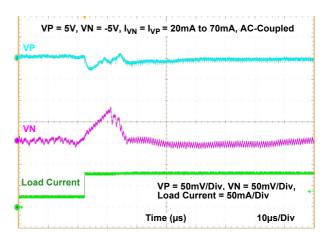

Figure 8. VP and VN Output Voltage Ripple - 50mA Load

Figure 9. VP and VN Output Voltage Ripple - 100mA Load

Figure 11. VP and VN Load Transient - Load Step Up

Figure 12. VP and VN Load Transient - Load Step Down

### 4. Application Information

### 4.1 I<sup>2</sup>C Digital Interface

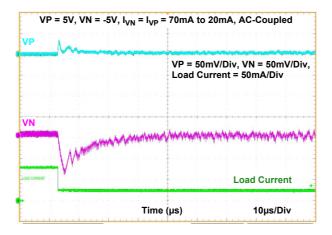

The ISL98607 uses a standard I<sup>2</sup>C interface bus for communication. The two-wire interface links a Master(s) and uniquely addressable Slave devices. The Master generates clock signals and is responsible for initiating data transfers. The serial clock is on the SCL line and the serial data (bi-directional) is on the SDA line. The ISL98607 supports clock rates up to 400kHz (Fast-Mode), and is backwards compatible with standard 100kHz clock rates (Standard-mode).

The SDA and SCL lines must be HIGH when the bus is free (not in use). An external pull-up resistor (typically  $2.2k\Omega$  to  $4.7k\Omega$ ) or current-source is required for SDA and SCL.

The ISL98607 meets standard I $^2$ C timing specifications. <u>Figure 13</u> and <u>Table 1 on page 10</u> show the standard timing definitions and specifications for I $^2$ C communication.

Figure 13. I<sup>2</sup>C Timing Definitions

Table 1. I<sup>2</sup>C Timing Characteristics

|                                                  |                     | Fast-M                 | ode | Standard- |      |      |

|--------------------------------------------------|---------------------|------------------------|-----|-----------|------|------|

| Parameter                                        | Symbol              | Min                    | Max | Min       | Max  | Unit |

| SCL Clock Frequency                              | f <sub>SCL</sub>    | 0                      | 400 | 0         | 100  | kHz  |

| Set-Up Time for a Start Condition                | t <sub>SU:STA</sub> | 0.6                    | -   | 4.7       | -    | μs   |

| Hold Time for a Start Condition                  | t <sub>HD:STA</sub> | 0.6                    | -   | 4.0       | -    | μs   |

| Set-Up Time for a Stop Condition                 | t <sub>SU:STO</sub> | 0.6                    | -   | 4.0       | -    | μs   |

| Bus Free Time between a Stop and Start Condition | t <sub>BUF</sub>    | 1.3                    | -   | 4.7       | -    | μs   |

| Data Set-up Time                                 | t <sub>SU:DAT</sub> | 100                    | -   | 250       | -    | ns   |

| Data Hold Time                                   | t <sub>HD:DAT</sub> | 0                      | -   | 0         | -    | μs   |

| Rise Time of SDA and SCL (Note 10)               | t <sub>r</sub>      | 20 + 0.1C <sub>b</sub> | 300 | -         | 1000 | ns   |

| Fall Time of SDA and SCL (Note 10)               | t <sub>f</sub>      | 20 + 0.1C <sub>b</sub> | 300 | -         | 300  | ns   |

| Capacitive Load on Each Bus Line (SDA/SCL)       | C <sub>b</sub>      | -                      | 400 | -         | 400  | pF   |

Note:

10. C<sub>b</sub> = total capacitance of one bus line in pF.

#### 4.1.1 Low-Power Mode

The I<sup>2</sup>C interface of ISL98607 remains active even when both ENN and ENP are LOW for up to 30ms. When ENN and ENP both remain LOW, and no I<sup>2</sup>C communication occurs for more than 30ms, the ISL98607 enters a low-power mode. This mode disables the I<sup>2</sup>C interface, but the interface is re-activated as soon as ISL98607 detects a logic LOW on SCL or SDA.

For the ISL98607, when the I<sup>2</sup>C interface is not used, both the SDA and SCL inputs must be tied HIGH (such as to VIN) or pulled-up to a logic HIGH level, to ensure the part enters the Low-Power consumption mode when ENN and ENP are held LOW longer than 30ms. This feature optimizes battery power saving in handheld products, such as, when the display system is put into a standby/sleep mode.

### 4.1.2 Start and Stop Condition

All I<sup>2</sup>C communication begins with a Start condition (indicating the beginning of a transaction) and ends with a Stop condition (signaling the end of the transaction).

A Start condition is signified by a HIGH-to-LOW transition on the serial data line (SDA) while the serial clock line (SCL) is HIGH. A Stop condition is signified by a LOW-to-HIGH transition on the SDA line while SCL is HIGH. See the timing specifications in <u>Table 1 on page 10</u>.

The Master always initiates Start and Stop conditions. After a Start condition, the bus is considered "busy." After a Stop condition, the bus is considered "free." The ISL98607 also supports repeated Starts, where the bus remains busy for the continued transaction(s).

### 4.1.3 Data Validity

The data on the SDA line must be stable (clearly defined as HIGH or LOW) during the HIGH period of the clock signal. The state of the SDA line can only change when the SCL line is LOW (except to create a Start or Stop condition). See the timing specifications in <u>Table 1</u>.

The voltage levels indicating a logical '0' (LOW) and logical '1' (HIGH) are determined by the  $V_{IL}$  and  $V_{IH}$  thresholds, respectively, see the "Electrical Specifications" table on page 7.

### 4.1.4 Byte Format

Every byte transferred on SDA must be 8 bits in length. After every byte of data sent by the transmitter there must be an Acknowledge bit (from the receiver) to signify that the previous 8 bits were transferred successfully. Data is always transferred on SDA with the Most Significant Bit (MSB) first. See <u>Acknowledge (ACK)</u>.

### 4.1.5 Acknowledge (ACK)

Each 8-bit data transfer is followed by an Acknowledge (ACK) bit from the receiver. The Acknowledge bit signifies that the previous 8 bits of data was transferred successfully (master-slave or slave-master).

When the Master sends data to the Slave (such as, during a WRITE transaction), after the 8th bit of a data byte is transmitted, the Master tri-states the SDA line during the 9th clock. The Slave device acknowledges that it received all 8 bits by pulling down the SDA line, generating an ACK bit.

When the Master receives data from the Slave (such as during a data READ transaction), after the 8th bit is transmitted, the Slave tri-states the SDA line during the 9th clock. The Master acknowledges that it received all 8 bits by pulling down the SDA line, generating an ACK bit.

### 4.1.6 Not Acknowledge (NACK)

A Not Acknowledge (NACK) is generated when the receiver does not pull-down the SDA line during the acknowledge clock (for example, SDA line remains HIGH during the 9th clock), which indicates to the Master that it can generate a Stop condition to end the transaction and free the bus.

A NACK can be generated for various reasons, for example:

- After an I<sup>2</sup>C device address is transmitted, there is NO receiver with that address on the bus to respond.

- The receiver is busy performing an internal operation (such as, reset, recall, etc), and cannot respond.

- The Master (acting as a receiver) needs to indicate the end of a transfer with the Slave (acting as a transmitter).

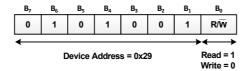

### 4.1.7 Device Address and R/W Bit

Data transfers follow the format shown in Figures 15 and 16. After a valid Start condition, the first byte sent in a transaction contains the 7-bit Device (Slave) Address plus a direction ( $R/\overline{W}$ ) bit. The Device Address identifies which device (of up to 127 devices on the  $I^2C$  bus) the Master wishes to communicate with.

After a Start condition, the ISL98607 monitors the first 8 bits (Device Address Byte) and checks for its 7-bit Device Address in the MSBs. If it recognizes the correct Device Address, it acknowledges and becomes ready for further communication. If it does not see its Device Address, it sits idle until another Start condition is issued on the bus.

To access the ISL98607, the 7-bit Device Address is 0x29 (0101001x), located in MSB bits  $<b_7:b_1>$ . The 8th bit of the Device Address byte (LSB bit  $<b_0>$ ) indicates the direction of transfer, READ or WRITE (R/W). A "0" indicates a WRITE operation (the Master transmits data to the ISL98607 (receiver)). A "1" indicates a Read operation (the Master receives data from the ISL98607 (transmitter)), see Figure 14.

Figure 14. Device Address Byte Format

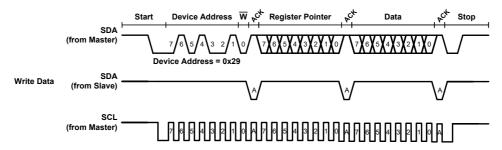

### 4.2 Write Operation

A WRITE sequence requires an I $^2$ C Start condition, followed by a valid Device Address Byte with the R/W bit set to '0', a valid Register Address Byte, a Data Byte, and a Stop condition. After each valid byte is sent, the ISL98607 (slave) responds with an ACK. When the Write transaction is completed, the Master should generate a Stop condition. For sent data to be latched by the ISL98607, the Stop condition should occur after a full byte (8-bits) is sent and ACK. If a Stop is generated in the middle of a byte transaction, the data is ignored. See <u>Figure 15</u> for the ISL98607 I $^2$ C Write protocol.

Figure 15. I<sup>2</sup>C Write Timing Diagram

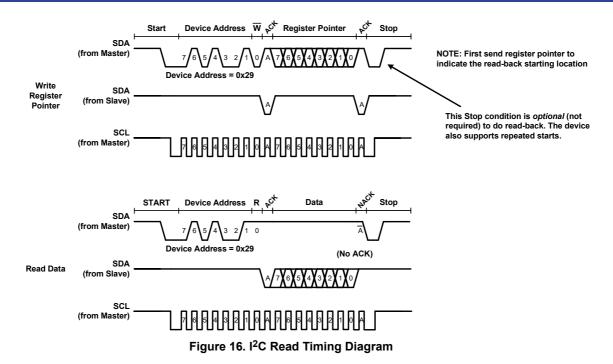

### 4.3 Read Operation

A READ sequence requires the Master to first write to the ISL98607 to indicate the Register Address/pointer to read from. Send a Start condition, followed by a valid Device Address Byte with the R/W set to '0', and then a valid Register Address Byte. Then the Master generates either a Repeat Start condition, or a Stop condition followed by a new Start condition, and a valid Device Address Byte with the R/W bit set to '1'. Finally, the ISL98607 is ready to send data to the Master from the requested Register Address.

The ISL98607 sends out the Data Byte by asserting control of the SDA pin while the Master generates clock pulses on the SCL pin. When transmission of the desired data is complete, the Master generates a NACK condition followed by a Stop condition, and this completes the I<sup>2</sup>C Read sequence. See <u>Figure 16 on page 13</u> for the ISL98607 I<sup>2</sup>C Read protocol.

### 4.4 Register Descriptions and Addresses

<u>Table 2 on page 15</u> contains the detailed register map, with descriptions and addresses for ISL98607 registers. Each volatile register is one byte (8-bit) in size. When writing data to adjust register settings using I<sup>2</sup>C, the data is latched-in after the 8th bit (LSB) is received.

The ISL98607 has default register settings that are always applied at IC power-ON or after a reset. In <u>Table 2</u>, the default register settings are indicated with **Bold** face text.

Reserved registers should only be written with the bit value indicated in the Register Map. Also, Register Addresses (pointers) not indicated in the Register Map are reserved and should not be written to.

Note: To clear/reset all the volatile registers to the default values, power cycle VIN.

### 4.5 Register Functions

The ISL98607 has various registers that can be used to adjust and control IC operating voltages, modes, thresholds, and sequences.

### **4.5.1 ENABLE**

The "ENABLE" register (Register Address 0x05) controls the enable/disable state of the boost (VBST), positive LDO (VP), and negative charge pump (VN) regulators, which sequences the regulators.

### 4.5.2 VBST OUT, VN OUT, VP OUT

The output voltages of VBST, VP, and VN regulators are changed using the registers VBST\_OUT (Register Address 0x06), VP\_OUT (Register Address 0x09), and VN\_OUT (Register Address 0x08), respectively.

The output voltages of all three regulators are changed from their default values using I<sup>2</sup>C. The VP regulator is programmed from +5V to +5.7V, the VN regulator is programmed from -5V to -5.7V, and the VBST regulator is programmed from +5.15V to +6.0V (each adjustable with 50mV step size). Do not use register settings that result in an expected output voltage above these maximum levels. To determine the expected output voltage for a specific register value, see "Output Voltage Calculation" on page 14.

Note: The output voltage registers should not be changed during their respective soft-start sequence.

#### 4.5.2.1 Output Voltage Calculation

The expected output voltage for each regulator is determined using <u>Equations 1</u> through <u>3</u>. For the calculations: VBST = 5.15V (typical) default, VP = +5V (typical) default, VN = -5V (typical) default. Note: VBST\_OUT, VP\_OUT, and VN\_OUT are the respective 5-bit register settings in decimal.

· Boost Output Voltage, VBST:

(EQ. 1)

$$VBST(V) = VBST + VBST_OUT \times 50mV$$

· LDO Output Voltage, VP

(EQ. 2)

$$VP(V) = VP + VP\_OUT \times 50mV$$

· Negative Charge Pump Output Voltage, VN:

(EQ. 3)

$$VN(V) = VN - VN_OUT \times 50 \text{mV}$$

**Example Calculations:**

If VBST\_OUT = 10 (dec):

$$VBST(V) = 5.15V + 10 \times 50mV = 5.65V$$

If VP OUT = 10 (dec):

$$VP(V) = 5V + 10 \times 50mV = 5.5V$$

If VN OUT = 10 (dec):

$$VN(V) = -5V - 10 \times 50 \text{mV} = -5.5V$$

### 4.5.3 VBST\_CNTRL, VN\_CNTRL

In addition to output voltages adjustments, key operation parameters are changed using the  $I^2C$  to optimize the ISL98607 performance.

The "VBST\_CNTRL" register (Register Address 0x0D) controls and optimizes boost PFM mode, boost FET slew rate, and switching frequency of the boost and charge pump.

The VN\_CNTRL register (Register Address 0x0F) enables and disables the PFM mode, and optimizes the charge pump PFM operation with adjustments to the PFM peak current, and pulse length.

### 4.5.4 **FAULT**

The "FAULT" register (Register Address 0x04) reads back the current fault status of the IC. The fault conditions that are read back by  $I^2C$  are:

- VBST undervoltage fault

- · VP undervoltage fault

- · VN undervoltage fault

- Over-Temperature Protection (OTP)

FAULT register bits <b $_3$ :b $_0$ > are reset by cycling the logic voltage on both the ENP and ENN pins simultaneously (set ENN = ENP = LOW, then ENN = ENP = HIGH) or power cycling VIN.

If FAULT register bit <b<sub>0</sub>> (OTP status bit) is latched HIGH for an OTP fault, it is reset after it is read twice by the I<sup>2</sup>C. A single I<sup>2</sup>C read returns the bit value (status), and a second read resets only the OTP bit.

### 4.6 Register Map

Table 2. Register Map

| REGISTER<br>ADDRESS<br>(HEX) | REGISTER<br>NAME | R/W | FUNCTION                                | BIT <b<sub>7&gt;</b<sub>                       | BIT <b<sub>6&gt;</b<sub>                                       | BIT <b<sub>5&gt;</b<sub>            | BIT <b<sub>4&gt;</b<sub>                                                                                                   | BIT <b<sub>3&gt;</b<sub>                                            | BIT <b<sub>2&gt;</b<sub>                                 | BIT <b<sub>1&gt;</b<sub>                                             | BIT <b<sub>0&gt;</b<sub>                      | DEFAUL<br>T VALUE<br>(HEX) | IC RESET                              |

|------------------------------|------------------|-----|-----------------------------------------|------------------------------------------------|----------------------------------------------------------------|-------------------------------------|----------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------|----------------------------------------------------------|----------------------------------------------------------------------|-----------------------------------------------|----------------------------|---------------------------------------|

| 0x04                         | FAULT            | R   | Fault Status<br>read-back               | Reserved<br>(Always set<br>to '0')             |                                                                | Not Used                            |                                                                                                                            | VP UVP:<br>0 = Output<br>Voltage OK<br>1 = UVP<br>Detect            | VN UVP:<br>0 = Output<br>Voltage OK<br>1 = UVP<br>Detect | VBST UVP:<br>0 = Output<br>Voltage OK<br>1 = UVP<br>Detect           | OTP:<br>0 = Temp<br>Ok<br>1 = OTP<br>detected | 0x00                       | Cycle ENN<br>and ENP, or<br>cycle VIN |

| 0x05                         | ENABLE           | R/W | IC Enable /<br>Sequencing               | Reserved<br>(Always set<br>to '0')             | VP Pull-down<br>resistor<br><b>0 = Enabled</b><br>1 = Disabled |                                     | Not Used                                                                                                                   |                                                                     | VP:<br>0 = Disable<br>1 = Enable                         | VN:<br>0 = Disable<br>1 = Enable                                     | VBST:<br>0 = Disable<br>1 = Enable            | 0x07                       | Cycle VIN                             |

| 0x06                         | VBST_OUT         | R/W | VBST Voltage<br>Adjustment              |                                                | Not Used                                                       |                                     | VBST_OUT <4:0>                                                                                                             |                                                                     | 0x00                                                     | Cycle VIN                                                            |                                               |                            |                                       |

| 80x0                         | VN_OUT           | R/W | VN Voltage<br>Adjustment                | Not Used                                       |                                                                |                                     |                                                                                                                            | VN_OUT <4:0>                                                        |                                                          |                                                                      |                                               | 0x00                       | Cycle VIN                             |

| 0x09                         | VP_OUT           | R/W | VP Voltage<br>Adjustment                |                                                | Not Used VP_OUT <4:                                            |                                     |                                                                                                                            | /P_OUT <4:0>                                                        |                                                          |                                                                      | 0x00                                          | Cycle VIN                  |                                       |

| 0x0D                         | VBST_<br>CNTRL   | R/W | VBST - boost<br>regulator<br>control    | (Always set to '00')<br>1 <b>1 = S</b><br>10 = |                                                                | slew rate  lowest Slow Fast castest | PFM mode (synchronou s PFM)  0 = Enable 1 = Disable 011 = 1.33 MHz  1 = Disable 102 = 1.45 MHz  1 = 1.60 MHz  1 = 2.00 MHZ |                                                                     |                                                          | witching                                                             | 0x34                                          | Cycle VIN                  |                                       |

| 0x0F                         | VN_<br>CNTRL     | R/W | VN - negative<br>charge pump<br>control |                                                | erved<br>set to '11')                                          | PFM Mode  0 = Enabled  1 = Disabled | PWM min<br>pulse length<br><b>1 = 94ns</b><br>0 = 125ns                                                                    | PFM peak cui<br>00 = 4μA<br>01 = 6μA<br><b>10 = 5μA</b><br>11 = 7μA | rent selection                                           | PFM Pulse le 00 = 188ns 01 = 219ns 10 = 250ns 11 = 50% sel frequency | ·                                             | 0xDA                       | Cycle VIN                             |

ISL98607

4. Application Information

#### Notes

- 11. Any Register Addresses/Pointers not indicated are Reserved Registers, and should not be used.

- 12. Bits labeled "Not Used" can be written and read from the volatile registers, but have no influence on the operation of the IC.

### 4.7 Output Voltage Setting

The VBST, VP, and VN output voltages are adjusted (from the default value) by the VBST\_OUT, VP\_OUT, and VN\_OUT volatile registers. <u>Equations 1</u> through <u>3</u> on <u>page 14</u> provide the relation between the value of the I<sup>2</sup>C registers and the respective output voltages.

### 4.8 VP and VN Headroom Voltage and Output Current

The VP and VN headroom voltage is defined as the difference between the VBST output voltage and:

- the maximum VP output voltage: VP headroom

- · the absolute value of the VN output voltage: VN headroom

The headroom voltage must be set high enough so that both the VP LDO and VN negative Charge Pump (CP) can maintain regulation. Primarily, the minimum headroom voltage is a function of the maximum application load current that the IC needs to support for at least few hundreds of microseconds. Fast output current peaks of only a few microseconds should not be considered (those instantaneous current peaks are supported by the output capacitors and not by the regulator).

Note: The headroom voltage should not be set overly high, because increasing headroom generally yields lower efficiency performance due to increased conduction losses.

For most applications, the ISL98607 default 150mV headroom voltage setting provides optimal performance for DC output current up to 100mA (maximum). For DC output current between 100mA and 150mA (maximum), the headroom voltage should be adjusted to 250mV. For example: if a maximum VP to VN load of 150mA is required, while VP = 5V and VN = -5V, then the minimum boost voltage should be set to VBST = 5.25V.

### 4.9 Regulator Output Enable/Disable

The boost converter, VBST, will be enabled whenever either ENP or ENN is HIGH, and the VBST enable bit <b<sub>0</sub>> in the ENABLE register is set to '1'. To disable the boost (and effectively VP and VN), ENN and ENP must be LOW, or its enable bit set to '0'.

The negative charge pump, VN, is enabled whenever ENN is HIGH, and the VN enable bit <br/> in the ENABLE register is set to '1'. To disable, ENN must be LOW, or its enable bit set to '0'.

The LDO, VP, is enabled whenever ENP is HIGH, and the VP enable bit  $\langle b_2 \rangle$  in the ENABLE register is set to '1'. To disable ENP must be LOW, or its enable bit set to '0'.

All the ENABLE register bits  $\langle b_2 : b_0 \rangle$  are set to '1' by default.

Various options to control the regulator output ON/OFF sequencing are possible with ISL98607, refer to the <u>"Enable Timing Control Options" on page 19</u> for more information.

Note, ENP and ENN are logic level inputs with HIGH/LOW thresholds defined by the  $V_{IH}/V_{IL}$  specifications, respectively. These inputs also have  $200k\Omega$  (typical) internal pull-down resistance to ground. If the pins are left hi-impedance, they will default to a LOW logic state. Refer to the "Logic" section of the "Electrical Specifications" table on page 7 for more information.

### 4.10 Negative Charge Pump Operation (VN)

The ISL98607 uses a negative charge pump with internal switches to create the VN voltage rail. The charge pump input voltage VBSTCP comes from the boost regulator output, VBST. The VBST voltage must be greater than the absolute value of the VN regulation voltage (for example, the headroom voltage has to be > 0V).

Regulation is achieved through a classic voltage mode architecture where an internally compensated gm amplifier compares the VN output voltage to the internal reference and sets a duty cycle. The duty cycle controls the amount of time the output capacitor is charged during each switching cycle. The maximum duty cycle is 50%. The charge pump output capacitor (placed on the VN pin) is charged and discharged through internal 450mA current sources to minimize system noise.

### 4.11 PFM

The ISL98607 features light-load Pulse Frequency Modulation (PFM) mode for both the boost regulator and charge pump to maximize efficiency at light loads.

The ISL98607 always uses PWM mode at heavy loading, but when PFM mode is enabled using the respective PFM mode enable/disable register bit, it automatically switches to PFM mode at light loads to optimize efficiency.

There is hysteresis built-in with the PFM transition for when the transition is from light to heavy or heavy to light loading, which prevents inadvertently going back and forth between PWM and PFM modes.

### 4.12 Fault Protection and Monitoring

The ISL98607 features extensive protections to automatically handle failure conditions and protect the IC and application from damage.

### 4.12.1 Overcurrent Protection (OCP)

The overcurrent protection limits the VBST nMOSFET current on a cycle-by-cycle basis. When the nMOSFET current reaches the current limit threshold, the nMOSFET is turned off for the remainder of that cycle. Overcurrent protection does not disable any of the regulators. When the fault is removed, the IC continues with normal operation.

### 4.12.2 Undervoltage Lockout (UVLO)

If the input voltage (VIN) falls below the  $V_{UVLO\_HYS}$  level of ~2.3V (typical), the VBST, VP, and VN regulators are disabled. All the rails restart with normal soft-start operation when the VIN input voltage is applied again (rising VIN >  $V_{UVLO}$ ). See the "Electrical Specifications" table on <u>page 6</u> for the UVLO specifications.

Note: The  $I^2C$  registers (logic) are not cleared/reset to default by the falling  $V_{IN}$  UVLO. The logic states are retained if  $V_{IN}$  remains above 2V (typical). When  $V_{IN}$  falls below 2V, all logic is reset.  $V_{IN}$  should fall below 2V (ideally to GND) before power is reapplied to ensures a full power cycle/reset of the device.

### 4.12.3 Over-Temperature Protection (OTP)

The ISL98607 has a hysteretic over-temperature protection threshold set at +130°C (typical). If this threshold is reached, the VBST, VP, and VN regulators are disabled immediately. As soon as temperature falls by 10°C (typical) then all the regulators automatically restart.

All register bits, except for bit  $<b_0>$  of the FAULT register (Register Address 0x04), remain unaffected during an OTP fault event. When an OTP event occurs, FAULT register bit  $<b_0>$  is latched to '1'. This bit is reset/cleared by cycling both ENN and ENP (set LOW, then HIGH) at the same time, or by cycling  $V_{IN}$  power. Bit  $<b_0>$  can also be reset after it is read twice by  $I^2C$ . A single  $I^2C$  read returns the bit value (status), and a second read resets only the OTP bit.

Output undervoltage protection is disabled during an OTP event. The output voltages decrease during an OTP event because the regulators are disabled, which does not trigger a UVP fault.

### 4.12.4 Undervoltage Protection (UVP)

The ISL98607 includes output undervoltage protection. Undervoltage protection disables the regulator whenever the output voltage of VBST or VP falls below 60% of its set/regulated voltage, or the output voltage of VN goes above 60% of its set/regulated voltage, for 100µs or more. If the output voltage exceeds the 60% condition for less than 100µs, no fault occurs.

Depending on which regulator(s) fault, bit(s) <b<sub>3</sub>>, <b<sub>2</sub>>, or <b<sub>1</sub>> in the FAULT register are latched to '1' for VP, VN, and VBST faults, respectively. The bit(s) are reset/cleared by cycling both ENN and ENP (set LOW, then HIGH) at the same time, or by cycling V<sub>IN</sub> power.

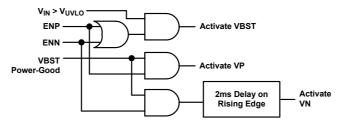

### 4.13 Power-ON/OFF Sequence

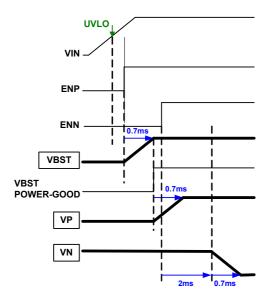

The boost regulator is activated when the  $V_{IN}$  input voltage is higher than the UVLO threshold, and either ENP or ENN are HIGH. The VP output is activated if ENP is HIGH and VBST has completed its soft-start. The VN charge pump is activated 2ms after VBST has completed soft-start, and the ENN has been pulled high, whichever comes later (see Figure 17).

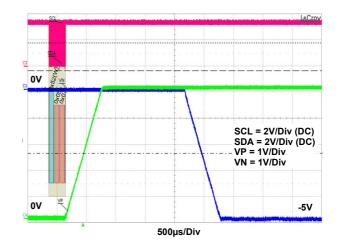

Figure 17. Power-On Logic Operation

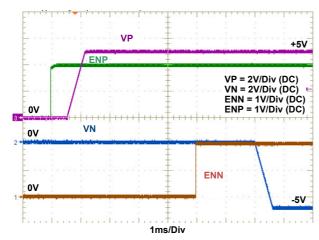

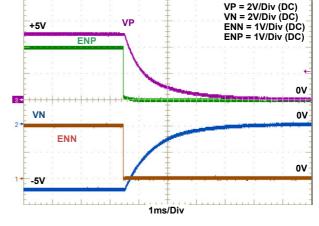

<u>Figure 18</u> shows power-ON timing for the case when ENN is pulled HIGH after ENP, and after the VBST soft-start is complete. <u>Figure 19</u> shows power-ON timing for the case when ENN is pulled HIGH after ENP, but before VBST has completed its soft-start.

Figure 18. Power-On Sequence - ENN Rising After VP Soft-Start Finished

Figure 19. Power-On Sequence - Both ENP and ENN Rising Before VBST Soft-Start Finished

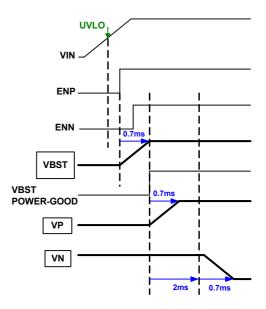

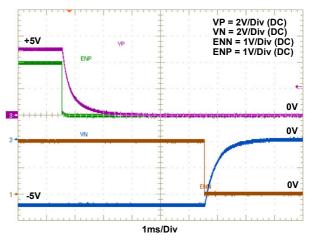

ENP or ENN going LOW shuts down VP or VN, respectively. If both ENP and ENN are pulled low, VP, VN, and VBST are all turned off even if  $V_{IN}$  is still above UVLO, see <u>Figure 20 on page 19</u>. If  $V_{IN}$  falls below UVLO while ENP and ENN are high, VP, VN, and VBST are turned off at the same time (see <u>Figure 21 on page 19</u>).

Figure 20. Power-Off Sequence - Activated by ENP and Figure 21. Power-Off Sequence - Activated by VIN Falling ENN When VIN is Above UVLO Below UVLO

The integrated discharge resistors on the VP and VN outputs are  $80\Omega$  (typical) and a  $35\Omega$  (typical), respectively. If the same output capacitor (value, size, rating) is used for VN and VP, the VN rail discharges faster than VP if they are both turned off at the same time, which is ideal for applications that require the VN rail to go down before VP at power-OFF.

### 4.14 Enable Timing Control Options

Three ways to control enable sequencing of the VP and VN regulators are:

- I<sup>2</sup>C control

- · Dual GPIO control

- Single GPIO control

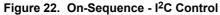

### 4.14.1 I<sup>2</sup>C Control

By using I<sup>2</sup>C, the sequencing of the VP and VN regulator is controlled by writing to the register 0x05. Bit  $<b_1>$  controls the VN regulator and  $<b_2>$  controls the VP regulator. Setting the bits to '1' enables the regulator and setting to '0' shuts off/disables the regulator. Delaying the writes for setting bit  $<b_1>$  and  $<b_2>$  (using separate I<sup>2</sup>C transactions) delays the turn-on and turn-off sequence of VP and VN accordingly.

<u>Figure 22 on page 20</u> shows a 4ms delay between when VP and VN turn on. The 4ms time is an example delay to show the power-ON sequencing possibility through I<sup>2</sup>C. This delay is set between the separate I<sup>2</sup>C writes to set the enable bits in register 0x05. If both enable bits were set to '1' in the same I<sup>2</sup>C transaction (same byte), and ENN and ENP are HIGH, both VP and VN regulators start at the same time (when the data is latched at the Stop condition).

<u>Figure 23</u> shows a 2.5ms delay between the VP and VN turn off. The 2.5ms time is an example delay to show the power-OFF sequencing possibility using I<sup>2</sup>C.

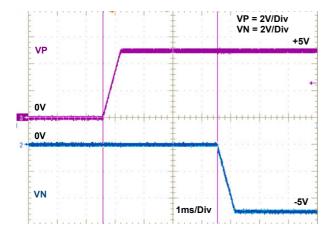

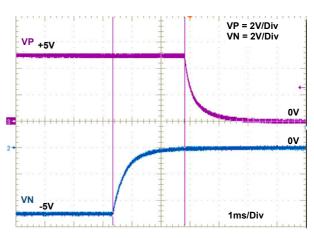

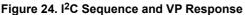

<u>Figures 24</u> (zoom in) and  $\underline{25}$  (zoom out) on <u>page 20</u> show a typical I<sup>2</sup>C data transfer to the ENABLE register. In this example, VP and VN regulators are enabled by writing data 0x07 to register address 0x05. The VP regulator is enabled first after the I<sup>2</sup>C Stop condition, followed by the VN regulator after the internal 2ms delay.

Figure 23. Off-Sequence - I<sup>2</sup>C Control

Figure 25. I<sup>2</sup>C Sequence and VP/VN Response

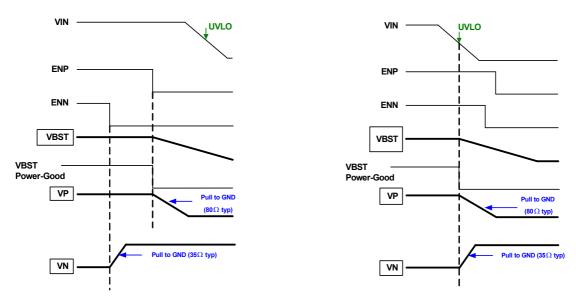

### 4.14.2 Separate ENP and ENN pins (2 GPIO control)

Using two separate GPIO's, and controlling the timing between the ENP and ENN pins, the turn on/off events can be controlled. The method to control turn on/off by GPIO is valid when the respective enable bits in the ENABLE register at Register Address 0x05 are set to '1' (default). So, this method is used at IC power-ON (no I<sup>2</sup>C communication is required).

By design, the VN regulator turns on 2ms after the ENN signal goes HIGH.

Figure 26 on page 21 shows a 5ms delay (example) between the ENP and ENN rise. VN turns on 2ms after ENN.

Figure 27 on page 21 shows a 5ms delay (example) between the ENP and ENN fall.

Figure 26. On Sequence - 2 GPIO Control

Figure 27. Off Sequence - 2 GPIO Control

### 4.14.3 Tie ENP and ENN together (1 GPIO control)

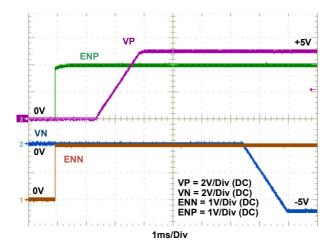

There is also an option to sequence the VN and VP regulators if there is only a single GPIO available in the system. The method to control turn on/off by GPIO is valid when the respective enable bits in the ENABLE register at Register Address 0x05 are set to '1' (default). So, this method is used at IC power-ON (no I<sup>2</sup>C communication is required).

If the ENP and ENN are tied together and both pulled HIGH, there is a default delay sequence in the IC. VP will come up first and after 2ms VN soft-starts. For turn off, both VN and VP start to shut down together, but the decay in the VP and VN voltage is controlled using the output capacitance value.

<u>Figure 28</u> shows turn on when the ENN and ENP pins are tied together. There is a 2ms delay between VP and VN turning on.

Figure 29 shows turn off when the ENN and ENP are tied together.

Figure 28. On Sequence - 1 GPIO Control

Figure 29. Off Sequence - 1 GPIO Control

### 4.15 VP Output Hi-Z Mode

The ISL98607 VP regulator can be configured in a Hi-Z mode for when the regulators are turned off. Using I<sup>2</sup>C, bit <becomes in the ENABLE register can be set to '1' to disable the internal pull-down resistor (this is Hi-Z Mode).

Configuring the VP regulator in Hi-Z mode prevents any leakage current flowing between VP and VN when the TFT-LCD is in sleep/standby mode, which minimizes the system power consumption.

### 4.16 Component Selection

The design of the boost converter is simplified by an internal compensation scheme, which allows easy system design without complicated calculations. Select component values using the following recommendations.

### 4.16.1 Input Capacitor

Renesas recommends that a 10µF X5R/X7R or equivalent ceramic capacitor is placed on the V<sub>IN</sub> input supply.

#### 4.16.2 Inductor

First, determine the minimum inductor saturation current required for the application.

The ISL98607 operates in Continuous Conduction Mode (CCM) at higher load current, and in Discontinuous Conduction Mode (DCM) and PFM mode at lighter loads.

In CCM, you can calculate the peak inductor current using Equations 4 through 8.

Given these parameters:

- Input Voltage = V<sub>IN</sub>

- Output Voltage = V<sub>O</sub>

- Duty Cycle = D

- Switching Frequency = f<sub>SW</sub>

- $t_{SW} = 1/f_{SW}$

Then the inductor ripple can be calculated as:

(EQ. 4)

$$\Delta I_{P-P} = (V_{IN})^*(D)/(L^*f_{SW}^*V_O)$$

where D = 1 -  $(V_{IN}/V_O)$ , then rewrite Equation 4:

(EQ. 5)

$$\Delta I_{P-P} = (V_{IN})*(V_O - V_{IN})/(L*f_{SW}*V_O)$$

The average inductor current is equal to the average input current, where  $I_{IAVG}$  can be calculated from the efficiency of the converter.

(EQ. 6)

$$I_{IAVG} = (V_O^*I_O)/(V_{IN}^*Efficiency)$$

To find the peak inductor current write the expression as:

(EQ. 7)

$$I_{Pk} = \Delta I_{P-P}/2 + I_{IAVG}$$

Substituting Equations 5 and 6 in Equation 7 calculates I<sub>Pk</sub>.

(EQ. 8)

$$I_{PK} = 0.5*V_{IN}*(V_{O} - V_{IN})/(L*f_{SW}*V_{O}) + (V_{O}*I_{O})/(V_{IN}*EFF)$$

Example:

Consider the following parameters in the steady-state boost regulator operating in CCM mode.

- $V_{IN} = 2.5V$

- $V_0 = 5.3V$

- $f_{SW} = 1.45MHz$

- Output load current = 100mA

- Efficiency = 80%

- $L = 2.2 \mu H$

Substituting previous parameters in **Equation 8** gives us:

$I_{Pk} = 453 \text{mA}$

The ISL98607 boost regulator operates in DCM and PFM mode at light load. In PFM mode, it uses a fixed peak inductor current of ~340mA.

To avoid the inductor core saturation, the saturation current of the inductor selected should be higher than the greater of the peak inductor current (for CCM) and the 340mA peak current in PFM mode.

The 340mA peak inductor current in PFM mode is optimized to provide maximum efficiency with a  $2.2\mu H$  inductor value. If a smaller inductor is used, less energy is delivered per cycle, the ISL98607 switches at a higher frequency, and the efficiency reduces. Increasing the inductor increases the energy delivered per pulse. However, for a given inductor size the DC-resistance (DCR) increases with inductor value, so the conduction losses increase. L =  $2.2\mu H$  is the optimal value for ISL98607.

<u>Table 3</u> shows the recommended inductors for typical ISL98607 applications (small size, handheld TFT-LCD display power).

Table 3. Recommended Inductors

| Inductor Part Number   | Inductance (µH) | DCR (mΩ) | I <sub>SAT</sub> (A) | Footprint Size |

|------------------------|-----------------|----------|----------------------|----------------|

| VLF302510MT-2R2M (TDK) | 2.2             | 70       | 1.23                 | 3025           |

| DFE252012C (Toko)      | 2.2             | 90       | 2.00                 | 2520           |

| TFM201610G-2R2M (TDK)  | 2.2             | 150      | 1.20                 | 2016           |

#### 4.16.3 Output Capacitor

The output capacitor supplies current to the load during transient conditions, and reduces the ripple voltage at the output. Output ripple voltage consists of two components:

- The voltage drop due to the inductor ripple current flowing through the ESR of the output capacitor.

- · Charging and discharging of the output capacitor.

For low ESR ceramic capacitors, the output ripple is dominated by the charging and discharging of the output capacitor. The voltage rating of the output capacitor should be greater than the maximum output voltage.

Note: Capacitors have a voltage coefficient. The effective capacitance reduces (derates) as the operating voltage/bias increases. Always see the manufacture's derating information to determine effective capacitance for the operating conditions.

The effective capacitance at the nominal output voltage should be  $2.2\mu F$  for VBST and VP regulator, and  $4.4\mu F$  for VN. Renesas recommends using a  $10\mu F$  X5R 10V or equivalent ceramic output capacitor for both VBST and VP outputs to provide a minimum of  $2.2\mu F$  effective capacitance. For the VN output, Renesas recommends use one or two  $10\mu F$  X5R 10V or equivalent ceramic output capacitors. Using two VN output capacitors results in <50mV peak-to-peak output voltage ripple with input voltages from 2.8V to 4.4V.

Table 4. Recommended Output Capacitors

| Capacitor Part Number      | Value (μF) | Size | Quantity                                                                                                                                     |

|----------------------------|------------|------|----------------------------------------------------------------------------------------------------------------------------------------------|

| GRM155R61A106ME11 (Murata) | 10         | 0402 | x5: C <sub>IN</sub> , C <sub>VBST</sub> , C <sub>VP</sub> , C <sub>VN</sub> , C <sub>CP</sub><br>x1: C <sub>VN</sub> (x2 for minimum ripple) |

| GRM188R61C475KAAJ (Murata) | 4.7        | 0603 | x5: C <sub>IN</sub> , C <sub>VBST</sub> , C <sub>VP</sub> , C <sub>VN</sub> , C <sub>CP</sub><br>x1: C <sub>VN</sub> (x2 for minimum ripple) |

### 5. General Layout Guidelines

When designing the printed circuit board (PCB) layout for the ISL98607, it is very important to understand the power requirements of the system. Some general best practices should be adhered to create an optimal PCB layout:

- 1. Careful consideration should be taken with any traces carrying AC signals. Keep AC current loops as short and as tight as possible. The current loop generates a magnetic field, which can couple to another conductor, inducing unwanted voltage. Place components such that current flows through them in a straight line as much as possible, which helps reduce the loop sizes and the EMI from the PCB.

- 2. If trace lengths are long, the resistance of the trace increases, can cause some reduction in IC efficiency, and cause system instability. Make the traces carrying power wide and short.

- 3. In discontinuous conduction mode, the direction of the current is interrupted every few cycles. This may result in large di/dt (transient load current). When injected in the ground plane the current may cause voltage drops, which can interfere with sensitive circuitry. Connect the analog ground and power ground of the IC very close to the IC to mitigate this issue.

- 4. One plane/layer in the PCB is recommended to be a dedicated ground plane. A large area of metal will have lower resistance, which reduces the return current impedance. More ground plane area minimizes parasitics and avoids corruption of the ground reference.

- 5. Isolate low frequency digital signals from any high frequency signals generated by switching frequency and harmonics. PCB traces should not cross each other. If they must cross due to the layout restriction, they must cross perpendicularly to reduce the magnetic field interaction.

- 6. The amount of copper that should be poured (thickness) depends upon the power requirement of the system. Insufficient copper increases resistance of the PCB, which increases heat dissipation.

- 7. Generally, vias should not be used to route high current paths.

- 8. While designing the layout of switched controllers, do not use the auto routing function of the PCB layout software. Auto routing connects the nets with same electrical name and does not account for ideal trace lengths and positioning.

### 5.1 ISL98607 Specific Layout Guidelines

- 1. Connect the input capacitor to the VIN pin with the smallest trace possible. This helps reject high frequency disturbances and promotes good regulation of the VBST, VP, and VN regulators.

- Connect the boost inductor to the LXP pin with a short and wide trace. Careful consideration should be made in selecting the inductor as it may cause electromagnetic interference, which could affect IC functionality. A shielded inductor is recommended.

- 3. The device has VBST and VBSTCP pins. VBST is the output of the boost regulator and VBSTCP is the input for the negative charge pump. Connect and short VBST and VBSTCP to each other on the PCB with a short and thick trace to avoid parasitic inductance and resistance. A 10μF/10V capacitor should be used on VBST. The distance of the capacitor from the VBST and VBSTCP pin is critical (it should be placed very close to the IC with a short and thick trace).

- 4. Renesas highly recommends that VN and VSUB are shorted together with a short and thick trace. It is recommended that 2x10μF/10V capacitors are placed on VN to minimize output ripple. Additionally, it helps minimize noise that may be coupled from the high-frequency ripple of the charge pump.

- 5. The VP regulator has two output pins (VP). Connect both pins directly with a short and thick trace.

- 6. Connect the IC Analog ground (AGND) and power ground (PGND) to each other. It is crucial to connect/short these two grounds very close to the IC.

- 7. Isolate the digital input pins, ENN and ENP, from the high di/dt and dv/dt signals. Otherwise, it may cause a glitch on those inputs.

- 8. I<sup>2</sup>C signals, if not used, should be tied to VIN.

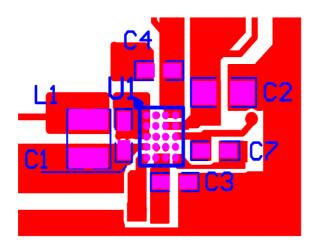

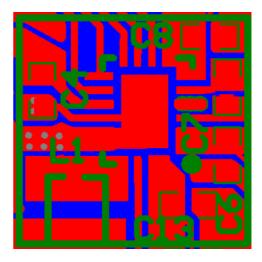

Figures 30 and 31 show the recommended PCB layout for a typical ISL98607 application.

Figure 30. ISL98607EIAZ Recommended PCB Layout

Figure 31. ISL98607IRTZ Recommended PCB Layout

ISL98607 6. Revision History

# 6. Revision History

| Rev. | Date     | Description                                                                                                                                     |

|------|----------|-------------------------------------------------------------------------------------------------------------------------------------------------|

| 1.00 | Jun.3.19 | Applied new template and formatting. Added Related Literature section. Added ISL98607IRTZ information throughout datasheet. Updated disclaimer. |

| 0.00 | Mar.8.13 | Initial release                                                                                                                                 |

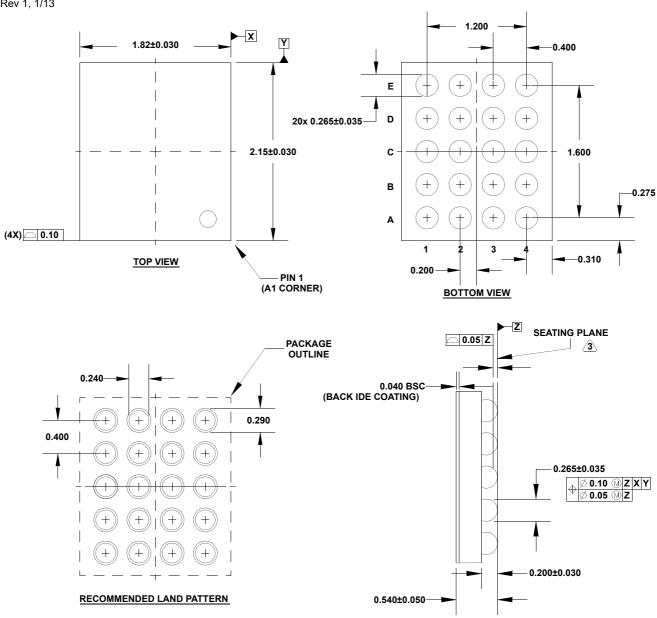

### 7. Package Outline Drawings

For the most recent package outline drawing, see <u>W4x5.20E</u>.

W4x5.20E 20 Ball Wafer Level Chip Scale Package (WLCSP) (BSC) Rev 1, 1/13

#### NOTES:

1. Dimensions and tolerance per ASME Y 14.5M - 1994.

SIDE VIEW

- A Primary datum Z and seating plane are defined by the spherical crowns of the bump.

- 4. Bump position designation per JESD 95-1, SPP-010.

- 5. There shall be a minimum clearance of 0.10mm between the edge of the bump and the body edge.

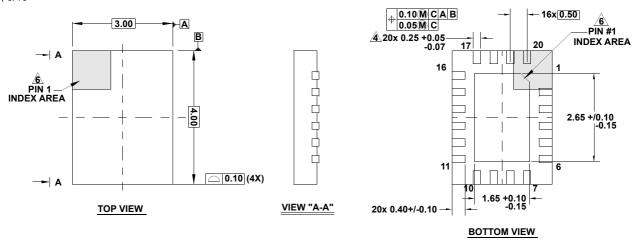

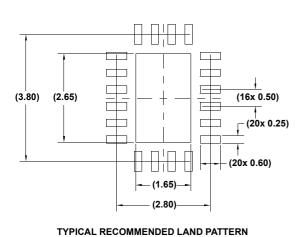

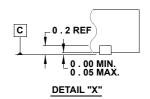

L20.3x4A 20 Lead Thin Quad Flat No-Lead Plastic Package Rev 0, 6/10

For the most recent package outline drawing, see <u>L20.3x4A</u>.

0.80 MAX

SEE DETAIL "X"

0.80 MAX

SEATING PLANE

0.008 C

SIDE VIEW

### NOTES:

- Dimensions are in millimeters.

Dimensions in ( ) for Reference Only.

- 2. Dimensioning and tolerancing conform to ASME Y14.5m-1994.

- 3. Unless otherwise specified, tolerance : Decimal  $\pm 0.05$

- Dimension applies to the metallized terminal and is measured between 0.15mm and 0.30mm from the terminal tip.

- 5. Tiebar shown (if present) is a non-functional feature.

- <u>6</u> The configuration of the pin #1 identifier is optional, but must be located within the zone indicated. The pin #1 identifier may be either a mold or mark feature.

- 7. JEDEC reference drawing: MO-220VEGD-NJI.

#### **Notice**

- Descriptions of circuits, software and other related information in this document are provided only to illustrate the operation of semiconductor products

and application examples. You are fully responsible for the incorporation or any other use of the circuits, software, and information in the design of your

product or system. Renesas Electronics disclaims any and all liability for any losses and damages incurred by you or third parties arising from the use of

these circuits, software, or information.

- 2. Renesas Electronics hereby expressly disclaims any warranties against and liability for infringement or any other claims involving patents, copyrights, or other intellectual property rights of third parties, by or arising from the use of Renesas Electronics products or technical information described in this document, including but not limited to, the product data, drawings, charts, programs, algorithms, and application examples.

- 3. No license, express, implied or otherwise, is granted hereby under any patents, copyrights or other intellectual property rights of Renesas Electronics or others

- 4. You shall not alter, modify, copy, or reverse engineer any Renesas Electronics product, whether in whole or in part. Renesas Electronics disclaims any and all liability for any losses or damages incurred by you or third parties arising from such alteration, modification, copying or reverse engineering.

- 5. Renesas Electronics products are classified according to the following two quality grades: "Standard" and "High Quality". The intended applications for each Renesas Electronics product depends on the product's quality grade, as indicated below.

- "Standard": Computers; office equipment; communications equipment; test and measurement equipment; audio and visual equipment; home electronic appliances; machine tools; personal electronic equipment; industrial robots; etc.

- "High Quality": Transportation equipment (automobiles, trains, ships, etc.); traffic control (traffic lights); large-scale communication equipment; key financial terminal systems; safety control equipment; etc.

Unless expressly designated as a high reliability product or a product for harsh environments in a Renesas Electronics data sheet or other Renesas Electronics document, Renesas Electronics products are not intended or authorized for use in products or systems that may pose a direct threat to human life or bodily injury (artificial life support devices or systems; surgical implantations; etc.), or may cause serious property damage (space system; undersea repeaters; nuclear power control systems; aircraft control systems; willtary equipment; etc.). Renesas Electronics disclaims any and all liability for any damages or losses incurred by you or any third parties arising from the use of any Renesas Electronics product that is inconsistent with any Renesas Electronics data sheet, user's manual or other Renesas Electronics document.

- 6. When using Renesas Electronics products, refer to the latest product information (data sheets, user's manuals, application notes, "General Notes for Handling and Using Semiconductor Devices" in the reliability handbook, etc.), and ensure that usage conditions are within the ranges specified by Renesas Electronics with respect to maximum ratings, operating power supply voltage range, heat dissipation characteristics, installation, etc. Renesas Electronics disclaims any and all liability for any malfunctions, failure or accident arising out of the use of Renesas Electronics products outside of such specified ranges.

- 7. Although Renesas Electronics endeavors to improve the quality and reliability of Renesas Electronics products, semiconductor products have specific characteristics, such as the occurrence of failure at a certain rate and malfunctions under certain use conditions. Unless designated as a high reliability product or a product for harsh environments in a Renesas Electronics data sheet or other Renesas Electronics document, Renesas Electronics products are not subject to radiation resistance design. You are responsible for implementing safety measures to guard against the possibility of bodily injury, injury or damage caused by fire, and/or danger to the public in the event of a failure or malfunction of Renesas Electronics products, such as safety design for hardware and software, including but not limited to redundancy, fire control and malfunction prevention, appropriate treatment for aging degradation or any other appropriate measures. Because the evaluation of microcomputer software alone is very difficult and impractical, you are responsible for evaluating the safety of the final products or systems manufactured by you.