# QUAD POWER AMPLIFIER WITH BUILT-IN VOLTAGE CONVERTER

PRODUCT PREVIEW

- DMOS POWER OUTPUT

- NON-SWITCHING HI-EFFICIENCY AMPLIFIER

- SWITCHING HIGH EFFICIENCY VOLTAGE CONVERTER

- HIGH OUTPUT POWER CAPABILITY 4x60W EIAJ/4Ω

- FULL I<sup>2</sup>C BUS DRIVING:

- ST-BY

- INDEPENDENT FRONT/REAR SOFT PLAY/MUTE

- SELECTABLE GAIN 26dB 12dB (FOR LOW NOISE LINE OUTPUT FUNCTION)

- HIGH EFFICIENCY ENABLE/DISABLE

- VOLTAGE CONVERTER ENABLE/DISABLE

- REGULATED VOLTAGE SELECTION

- SWITCHING FREQUENCY SELECTION

- HARDWARE MUTE FUNCTION

- FULL FAULT PROTECTION

- DC OFFSET DETECTION

- FOUR INDEPENDENT SHORT CIRCUIT PROTECTION

- CLIPPING DETECTOR WITH SELECTABLE THRESHOLD (1%/10%) VIA I<sup>2</sup>C BUS

#### MULTIPOWER BCD TECHNOLOGY

#### MOSFET OUTPUT POWER STAGE

**ORDERING NUMBER: TDA7565**

#### DESCRIPTION

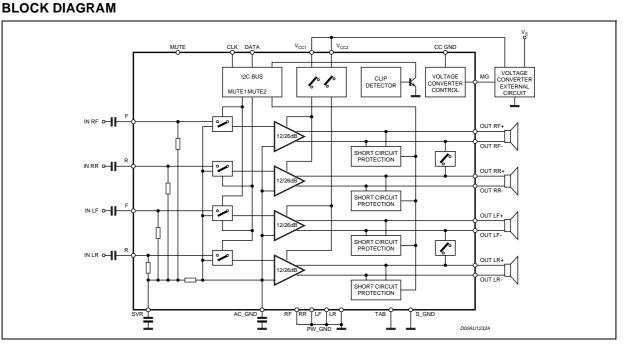

The TDA7565 is a new BCD technology QUAD BRIDGE type of car radio amplifier in Flexiwatt27 package specially intended for car radio applications. Thanks to the DMOS output stage the TDA7565 has a very low distortion allowing a clear powerful sound. The built-in voltage converter control block assures a very high output power with an extremely low number of added components. The dissipated power under average listening condition is alligned to the conventional solutions (4x40W).

#### September 2003

This is preliminary information on a new product now in development. Details are subject to change without notice.

# TDA7565

## **ABSOLUTE MAXIMUM RATINGS**

| Symbol                            | Parameter                                      | Value      | Unit |

|-----------------------------------|------------------------------------------------|------------|------|

| Vopc OFF                          | Operating Supply Voltage, converter OFF        | 18         | V    |

| V <sub>opc ON</sub>               | Operating Supply Voltage, converter ON         | 25         | V    |

| Vs                                | DC Supply Voltage                              | 28         | V    |

| V <sub>peak</sub>                 | Peak Supply Voltage (for t = 50ms)             | 50         | V    |

| V <sub>CK</sub>                   | CK pin Voltage                                 | 6          | V    |

| Vdata                             | Data Pin Voltage                               | 6          | V    |

| Ι <sub>Ο</sub>                    | Output Peak Current (not repetitive t = 100µs) | 8          | A    |

| Ι <sub>Ο</sub>                    | Output Peak Current (repetitive f > 10Hz)      | 6          | А    |

| P <sub>tot</sub>                  | Power Dissipation T <sub>case</sub> = 70°C     | 80         | W    |

| T <sub>stg</sub> , T <sub>j</sub> | Storage and Junction Temperature               | -55 to 150 | °C   |

## THERMAL DATA

| Symbol                 | Description                           | Value | Unit |

|------------------------|---------------------------------------|-------|------|

| R <sub>th j-case</sub> | Thermal Resistance Junction-case Max. | 1     | °C/W |

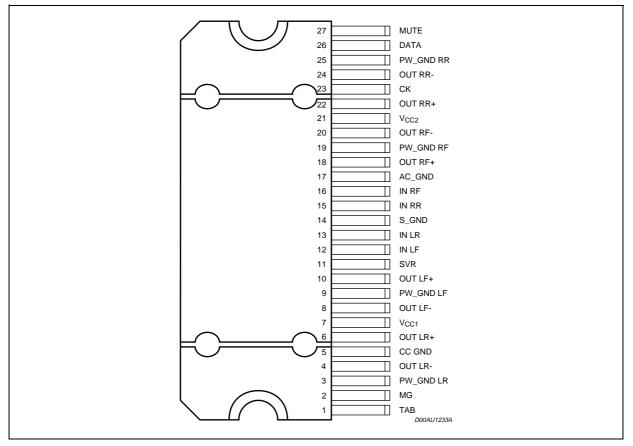

# **PIN CONNECTION**

# ELECTRICAL CHARACTERISTICS

(Refer to the test circuit,  $V_S = 13.5V$ ;  $R_L = 4\Omega$ ; f = 1KHz; Voltage converter Disabled (VC<sub>Off</sub>);  $T_{amb} = 25^{\circ}C$ ; unless otherwise specified.)

| Symbol                 | Parameter                                            | Test Condition                                                                   | Min. | Тур.                | Max. | Unit        |

|------------------------|------------------------------------------------------|----------------------------------------------------------------------------------|------|---------------------|------|-------------|

| POWER A                | MPLIFIER                                             |                                                                                  |      |                     |      |             |

| Vs                     | Supply Voltage Range                                 |                                                                                  | 8    |                     | 18   | V           |

| l <sub>d</sub>         | Total Quiescent Drain Current                        |                                                                                  |      | 180                 | 300  | mA          |

| l <sub>d</sub>         | Total Quiescent Drain Current<br>(VC <sub>on</sub> ) |                                                                                  |      | TBD                 |      | mA          |

| Po                     | Output Power                                         | EIAJ (V <sub>S</sub> = 13.7V)                                                    |      | 35                  |      | W           |

|                        | $(VC_{off})$<br>V = 14.4V                            | THD = 10%<br>THD = 1%                                                            |      | 25<br>20            |      | W<br>W      |

| Po                     | Output Power                                         | EIAJ (V <sub>S</sub> = 13.7V)                                                    |      | 60                  |      | W           |

|                        | (VC <sub>on</sub> )                                  | THD = 10%                                                                        |      | 40                  |      | W           |

|                        | V = 14.4V                                            | THD = 1%                                                                         |      | 31                  |      | W           |

| THD                    | Total Harmonic Distortion                            | P <sub>O</sub> = 1W to 12W; STDMODE<br>HE MODE; PO = 1-2W<br>HE MODE; PO = 4-12W |      | 0.03<br>0.03<br>0.1 | 0.1  | %<br>%<br>% |

|                        |                                                      | P <sub>O</sub> = 1-12W, f = 10kHz                                                |      | 0.15                | 0.5  | %           |

| CT                     | Cross Talk                                           | $f = 1 KHz$ to 10KHz, $R_G = 600\Omega$                                          | 50   | 55                  |      | dB          |

| R <sub>IN</sub>        | Input Impedance                                      |                                                                                  | 60   | 100                 | 130  | KΩ          |

| G <sub>V1</sub>        | Voltage Gain 1                                       |                                                                                  | 25.5 | 26                  | 26.5 | dB          |

| $\Delta G_{V1}$        | Voltage Gain Match 1                                 |                                                                                  | -1   |                     | 1    | dB          |

| G <sub>V2</sub>        | Voltage Gain 2                                       |                                                                                  | 11.5 | 12                  | 12.5 | dB          |

| $\Delta G_{V2}$        | Voltage Gain Match 2                                 |                                                                                  | -1   |                     | 1    | dB          |

| E <sub>IN1</sub>       | Output Noise Voltage 1                               | $R_g = 600\Omega; G_V = 26dB$<br>filter 20Hz to 22kHz                            |      | 60                  | 100  | μV          |

| E <sub>IN2</sub>       | Output Noise Voltage 2                               | $R_g = 600\Omega$ ; $G_V = 26dB$<br>filter 20Hz to 12kHz                         |      | 15                  | 20   | μV          |

| SVR                    | Supply Voltage Rejection                             | f = 100Hz to 10kHz; V <sub>r</sub> = 1Vpk;<br>R <sub>g</sub> = 600Ω              | 50   | 60                  |      | dB          |

| BW                     | Power Bandwidth                                      | (-3dB)                                                                           | 75   |                     |      | KHz         |

| A <sub>SB</sub>        | Stand-by Attenuation                                 |                                                                                  | 70   | 100                 |      | dB          |

| I <sub>SB</sub>        | Stand-by Current                                     |                                                                                  |      |                     | 100  | μΑ          |

| AM                     | Mute Attenuation                                     |                                                                                  | 70   | 90                  |      | dB          |

| Vos                    | Offset Voltage                                       | Mute & Play                                                                      | -100 |                     | 100  | mV          |

| VAM                    | Min. Supply Voltage Threshold                        |                                                                                  | 6.5  | 7                   | 7.5  | V           |

|                        | Slew Rate                                            |                                                                                  | 1.5  |                     |      | V/µs        |

| TON                    | Turn on Delay                                        | D2/D1 (IB1) 0 to 1                                                               |      | 10                  | 20   | ms          |

| T <sub>OFF</sub>       | Turn off Delay                                       | D2/D1 (IB1) 1 to 0                                                               |      | 10                  | 20   | ms          |

|                        | Thermal Foldback Junction<br>Temperature             |                                                                                  | 155  | 170                 | 185  | °C          |

| CD <sub>THD</sub>      | Clip Det THD level                                   | D0 (IB1) = 0                                                                     | 0    | 1                   | 2    | %           |

|                        |                                                      | D0 (IB1) = 1                                                                     | 5    | 10                  | 15   | %           |

| Vo                     | Offset Detection                                     | Power Amplifier = play<br>AC Input = 0                                           | ±1.5 | ±2                  | ±2.5 | V           |

| T <sub>hw</sub>        | Thermal Warning                                      |                                                                                  |      | 165                 |      | °C          |

| I <sup>2</sup> C BUS I | NTERFACE                                             |                                                                                  |      |                     |      |             |

| f <sub>SCL</sub>       | Clock Frequency                                      |                                                                                  |      |                     | 400  | KHz         |

| VIL                    | Input Low Voltage                                    |                                                                                  |      |                     | 1.5  | V           |

| VIH                    | Input High Voltage                                   |                                                                                  | 2.3  |                     |      | V           |

# ELECTRICAL CHARACTERISTICS (continua)

(Refer to the test circuit,  $V_S = 13.5V$ ;  $R_L = 4\Omega$ ; f = 1KHz; Voltage converter Disabled (VC<sub>Off</sub>);  $T_{amb} = 25^{\circ}C$ ; unless otherwise specified.)

| Symbol                       | Parameter                                                  | Test Condition                                                                                                       | Min. | Тур.                       | Max. | Unit                     |

|------------------------------|------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------|------|----------------------------|------|--------------------------|

| V <sub>Min(pin27)</sub>      | Mute in Threshold Voltage                                  | Amp. Mute                                                                                                            |      |                            | 1.5  | V                        |

| V <sub>Mout</sub> (pin27)    | Mute out Threshold Voltage                                 |                                                                                                                      | 3.5  |                            |      | V                        |

| A <sub>M(pin 27)</sub>       | Mute Attenuation                                           |                                                                                                                      | 80   | 90                         |      |                          |

| VOLTAGE                      | CONVERTER                                                  | 1                                                                                                                    |      |                            |      |                          |

| Vcc1,<br>Vcc2                | Converter Output Voltage<br>(VC = ON)                      |                                                                                                                      |      | 15<br>16.5<br>17.5<br>18.5 |      | V<br>V<br>V<br>V         |

| Fs                           | Voltage Converter Switching<br>Frequency                   | D6 (IB1) = 0; D7 (IB1) = 0<br>D6 (IB1) = 1; D7 (IB1) = 0<br>D6 (IB1) = 0; D7 (IB1) = 1<br>D6 (IB1) = 1; D7 (IB1) = 1 |      | 100<br>150<br>260<br>400   |      | kHz<br>kHz<br>kHz<br>kHz |

| Vmgl                         | Mos Gate Output Low Voltage                                | lo = 250mA                                                                                                           |      |                            | 1    | V                        |

| Vmgh                         | Mos Gate Output High Voltage                               | lo = 20mA                                                                                                            |      | 10.5                       |      | V                        |

|                              |                                                            | lo = 200mA                                                                                                           |      | 10                         |      | V                        |

| Vmgclamp                     | Mos Gate Output Clamp Voltage                              | lo = 5mA                                                                                                             |      | TBD                        |      | V                        |

| tf                           | Fall Time                                                  | Co = 1nF                                                                                                             |      | 20                         |      | ns                       |

| tr                           | Rise Time                                                  | Co = 1nF                                                                                                             |      | 50                         |      | ns                       |

| Vmgl<br>(VC <sub>off</sub> ) | Mos Gate Output Voltage with<br>Voltage Converter Disabled | lo = 5mA                                                                                                             |      |                            | 0.5  | V                        |

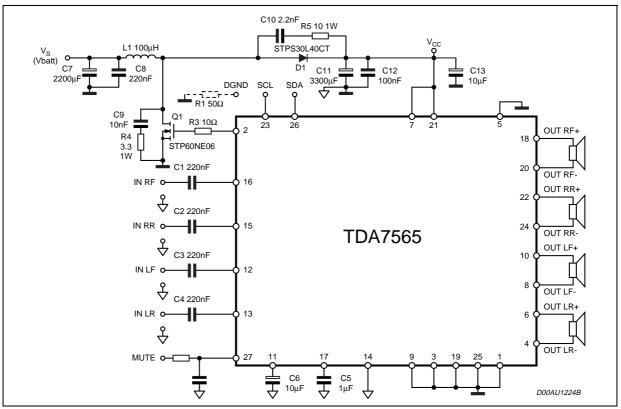

# Figure 1. Demoboard Schematic

# I<sup>2</sup>C BUS INTERFACE

Data transmission from microprocessor to the TDA7565 and viceversa takes place through the 2 wires I<sup>2</sup>C BUS interface, consisting of the two lines SDA and SCL (pull-up resistors to positive supply voltage must be connected).

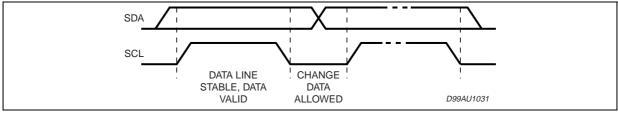

## **Data Validity**

As shown by fig. 2, the data on the SDA line must be stable during the high period of the clock. The HIGH and LOW state of the data line can only change when the clock signal on the SCL line is LOW.

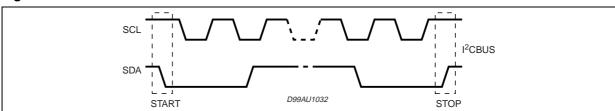

## **Start and Stop Conditions**

As shown by fig. 3 a start condition is a HIGH to LOW transition of the SDA line while SCL is HIGH. The stop condition is a LOW to HIGH transition of the SDA line while SCL is HIGH.

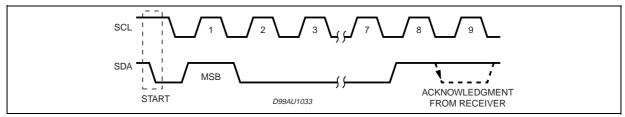

#### **Byte Format**

Every byte transferred to the SDA line must contain 8 bits. Each byte must be followed by an acknowledge bit. The MSB is transferred first.

## Acknowledge

The transmitter<sup>\*</sup> puts a resistive HIGH level on the SDA line during the acknowledge clock pulse (see fig. 22). The receiver<sup>\*\*</sup> the acknowledges has to pull-down (LOW) the SDA line during the acknowledge clock pulse, so that the SDA line is stable LOW during this clock pulse.

## \* Transmitter

master ( $\mu P$ ) when it writes an address to the TDA7565

slave (TDA7565) when the  $\mu P$  reads a data byte from TDA7565

## \*\* Receiver

slave (TDA7565) when the  $\mu$ P writes an address to the TDA7565 master ( $\mu$ P) when it reads a data byte from TDA7565

# Figure 2. Data Validity on the I<sup>2</sup>C BUS

## Figure 3.

## Figure 4.

# SOFTWARE SPECIFICATIONS

All the functions of the TDA7565 are activated by  $\mathsf{I}^2\mathsf{C}$  interface.

The bit 0 of the "ADDRESS BYTE" defines if the next bytes are write instruction (from  $\mu$ P to TDA7565) or read instruction (from TDA7565 to  $\mu$ P).

| D7      | Address bit                                                     |

|---------|-----------------------------------------------------------------|

| D6      | Address bit                                                     |

| D5      | Address bit                                                     |

| D4      | Address bit                                                     |

| D3      | Address bit                                                     |

| D2      | Address bit                                                     |

| D1      | Address bit                                                     |

| D0(R/W) | Read/Write bit<br>0 = Write instruction<br>1 = read instruction |

If R/W = 0, the  $\mu$ P sends 2 "Instruction Bytes": IB1 and IB2.

#### IB1

| D7 | Sel Freq Switch 1                                                       |

|----|-------------------------------------------------------------------------|

| D6 | Sel Freq Switch 2                                                       |

| D5 | Offset Detection start (D5 = 1)<br>Offset Detection stop (D5 = 0) (off) |

| D4 | Front Channel<br>Gain = $26dB (D4 = 0)$<br>Gain = $12dB (D4 = 1)$       |

| D3 | Rear Channel<br>Gain = $26dB (D3 = 0)$<br>Gain = $12dB (D3 = 1)$        |

| D2 | Mute front channels (D2 = 0)<br>Unmute front channels (D2 = 1)          |

| D1 | Mute rear channels (D1 = 0)<br>Unmute rear channels (D1 = 1)            |

| D0 | CD 1% (D0 = 0)<br>CD 10% (D0 = 1)                                       |

#### IB2

| D7 | Voltage Converter Enabled (D7 = 1)<br>Voltage Converter Disabled (D7 = 0)                                           |

|----|---------------------------------------------------------------------------------------------------------------------|

| D6 | Regulated voltage selection 1                                                                                       |

| D5 | Test Speed                                                                                                          |

| D4 | Stand-by on - Amplifier not working - (D4 = 0)<br>Stand-by off - Amplifier working - (D4 = 1)                       |

| D3 | Regulated voltage selection 0)                                                                                      |

| D2 | To be forced to "Level 1"                                                                                           |

| D1 | Right Channel<br>Power amplifier working in standard mode (D1 = 0)<br>Power amplifier working in HiEff mode(D1 = 1) |

| D0 | Left Channel<br>Power amplifier working in standard mode (D0 = 0)<br>Power amplifier working in HiEff mode(D0 = 1)  |

# DB1

| D7 | Thermal Warning                |

|----|--------------------------------|

| D6 | X                              |

| D5 | X                              |

| D4 | X                              |

| D3 | X                              |

| D2 | Offset (LF)                    |

| D1 | Short Circuit Protection (CH1) |

| D0 | X                              |

# DB2

| D7 | Off Status                     |

|----|--------------------------------|

| D6 | X                              |

| D5 | Clip Detector Output           |

| D4 | X                              |

| D3 | X                              |

| D2 | Offset (LR)                    |

| D1 | Short Circuit Protection (CH2) |

| D0 | X                              |

# DB3

| D7 | St-By Status                   |

|----|--------------------------------|

| D6 | X                              |

| D5 | X                              |

| D4 | X                              |

| D3 | X                              |

| D2 | Offset (RF)                    |

| D1 | Short Circuit Protection (CH3) |

| D0 | X                              |

# DB4

| D7 | X                              |

|----|--------------------------------|

| D6 | X                              |

| D5 | X                              |

| D4 | X                              |

| D3 | X                              |

| D2 | Offset (RR)                    |

| D1 | Short Circuit Protection (CH4) |

| D0 | X                              |

# TDA7565

# Examples of bytes sequence

1 - Turn-On of the power amplifier with 26dB gain, mute on, diagnostic defeat, HighEff mode, voltage converter disabled.

| Start | Address byte with D0 = 0 | ACK | IB1      | ACK | IB2      | ACK | STOP |

|-------|--------------------------|-----|----------|-----|----------|-----|------|

|       |                          |     | XX00X000 |     | 0XX1XX10 |     |      |

# 2 - Turn-Off of the power amplifier

| Ī | Start | Address byte with D0 = 0 | ACK | IB1      | ACK | IB2      | ACK | STOP |

|---|-------|--------------------------|-----|----------|-----|----------|-----|------|

| _ |       |                          |     | XXXXXXXX |     | XXX0XXX0 |     |      |

#### 4 - Offset detection procedure start

| Ī | Start | Address byte with D0 = 0 | ACK | IB1      | ACK | IB2      | ACK | STOP |

|---|-------|--------------------------|-----|----------|-----|----------|-----|------|

| - |       |                          |     | XX1XX11X |     | XXX1XXX0 |     |      |

4 - Offset detection procedure stop and reading operation.

| Start Address byte with D0 = 1 | ACK | DB1 | STOP |

|--------------------------------|-----|-----|------|

|--------------------------------|-----|-----|------|

- The purpose of this test is to check if a D.C. offset (2V typ.) is present on the outputs, produced by input capacitor with anomalous leackage current or humidity between pins.

- The delay from 3 to 4 can be selected by software, starting from T.B.D. ms

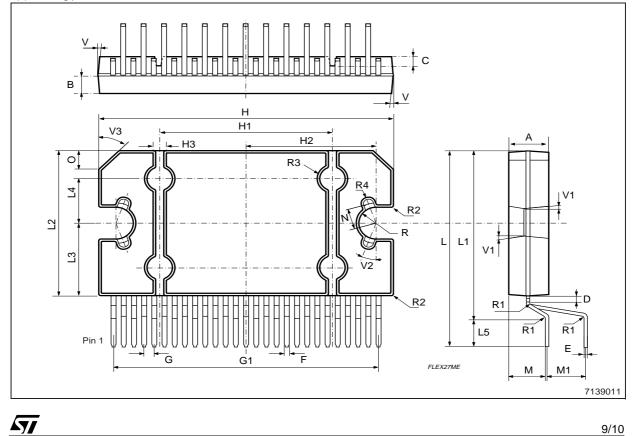

| DIM.   | mm            |       |       |       | inch  |       |  |  |

|--------|---------------|-------|-------|-------|-------|-------|--|--|

|        | MIN.          | TYP.  | MAX.  | MIN.  | TYP.  | MAX.  |  |  |

| А      | 4.45          | 4.50  | 4.65  | 0.175 | 0.177 | 0.183 |  |  |

| В      | 1.80          | 1.90  | 2.00  | 0.070 | 0.074 | 0.079 |  |  |

| С      |               | 1.40  |       |       | 0.055 |       |  |  |

| D      | 0.75          | 0.90  | 1.05  | 0.029 | 0.035 | 0.041 |  |  |

| E      | 0.37          | 0.39  | 0.42  | 0.014 | 0.015 | 0.016 |  |  |

| F (1)  |               |       | 0.57  |       |       | 0.022 |  |  |

| G      | 0.80          | 1.00  | 1.20  | 0.031 | 0.040 | 0.047 |  |  |

| G1     | 25.75         | 26.00 | 26.25 | 1.014 | 1.023 | 1.033 |  |  |

| H (2)  | 28.90         | 29.23 | 29.30 | 1.139 | 1.150 | 1.153 |  |  |

| H1     |               | 17.00 |       |       | 0.669 |       |  |  |

| H2     |               | 12.80 |       |       | 0.503 |       |  |  |

| H3     |               | 0.80  |       |       | 0.031 |       |  |  |

| L (2)  | 22.07         | 22.47 | 22.87 | 0.869 | 0.884 | 0.904 |  |  |

| L1     | 18.57         | 18.97 | 19.37 | 0.731 | 0.747 | 0.762 |  |  |

| L2 (2) | 15.50         | 15.70 | 15.90 | 0.610 | 0.618 | 0.626 |  |  |

| L3     | 7.70          | 7.85  | 7.95  | 0.303 | 0.309 | 0.313 |  |  |

| L4     |               | 5     |       |       | 0.197 |       |  |  |

| L5     |               | 3.5   |       |       | 0.138 |       |  |  |

| М      | 3.70          | 4.00  | 4.30  | 0.145 | 0.157 | 0.169 |  |  |

| M1     | 3.60          | 4.00  | 4.40  | 0.142 | 0.157 | 0.173 |  |  |

| Ν      |               | 2.20  |       |       | 0.086 |       |  |  |

| 0      |               | 2     |       |       | 0.079 |       |  |  |

| R      |               | 1.70  |       |       | 0.067 |       |  |  |

| R1     |               | 0.5   |       |       | 0.02  |       |  |  |

| R2     |               | 0.3   |       |       | 0.12  |       |  |  |

| R3     |               | 1.25  |       |       | 0.049 |       |  |  |

| R4     |               | 0.50  |       |       | 0.019 |       |  |  |

| V      | 5° (Typ.)     |       |       |       |       |       |  |  |

| V1     | 3° (Тур.)     |       |       |       |       |       |  |  |

| V2     |               |       |       |       |       |       |  |  |

| V3     | /3 45° (Typ.) |       |       |       |       |       |  |  |

# **OUTLINE AND MECHANICAL DATA**

(1): dam-bar protusion not included(2): molding protusion included

Information furnished is believed to be accurate and reliable. However, STMicroelectronics assumes no responsibility for the consequences of use of such information nor for any infringement of patents or other rights of third parties which may result from its use. No license is granted by implication or otherwise under any patent or patent rights of STMicroelectronics. Specifications mentioned in this publication are subject to change without notice. This publication supersedes and replaces all information previously supplied. STMicroelectronics products are not authorized for use as critical components in life support devices or systems without express written approval of STMicroelectronics.

> The ST logo is a registered trademark of STMicroelectronics. All other names are the property of their respective owners

> > © 2003 STMicroelectronics - All rights reserved

## STMicroelectronics GROUP OF COMPANIES

Australia - Belgium - Brazil - Canada - China - Czech Republic - Finland - France - Germany - Hong Kong - India - Israel - Italy - Japan -Malaysia - Malta - Morocco - Singapore - Spain - Sweden - Switzerland - United Kingdom - United States

www.st.com

This datasheet has been download from:

www.datasheetcatalog.com

Datasheets for electronics components.